Section 13 Direct Memory Access Controller (DMAC)

Rev. 4.00 Sep. 14, 2005 Page 427 of 982

REJ09B0023-0400

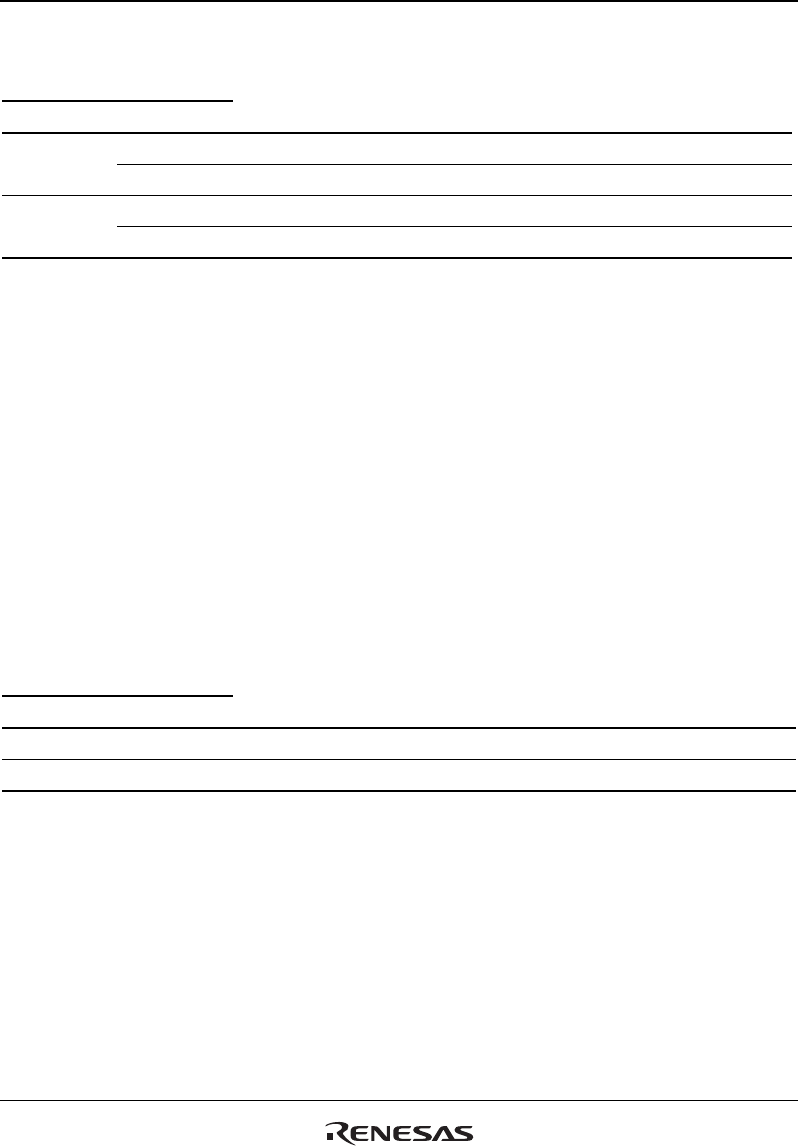

Table 13.5 Selecting External Request Detection with Dl, DS Bits

CHCR

DL DS Detection of External Request

0 Low level detection 0

1 Falling edge detection

0 High level detection 1

1 Rising edge detection

When DREQ is accepted, the DREQ pin becomes request accept disabled state (non-sensitive

period). After issuing acknowledge signal DACK for the accepted DREQ, the DREQ pin again

becomes request accept enabled state.

When DREQ is used by level detection, there are following two cases by the timing to detect the

next DREQ after outputting DACK.

Overrun0: Transfer is aborted after the same number of transfer has been performed as requests.

Overrun1: Transfer is aborted after transfers have been performed for (the number of requests

plus 1) times.

The DO bit in CHCR selects this overrun 0 or overrun 1.

Table 13.6 Selecting External Request Detection with DO Bit

CHCR_0 or CHCR_1

DO External Request

0 Overrun 0

1 Overrun 1