Section 13 Direct Memory Access Controller (DMAC)

Rev. 4.00 Sep. 14, 2005 Page 448 of 982

REJ09B0023-0400

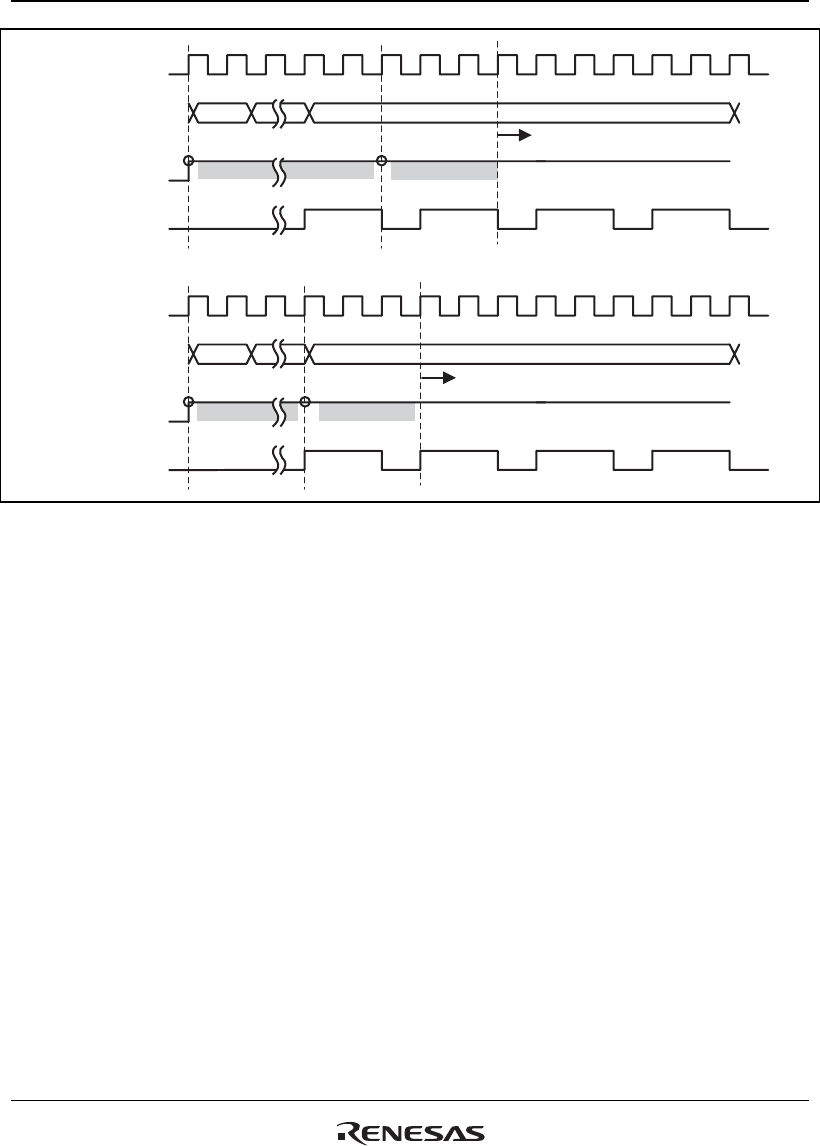

CPU

DMAC write

Non-sensitive period

1st acceptance 2nd acceptance

3rd acceptance possible

Non-sensitive period

CPU

DMAC write

Non-sensitive period

1st acceptance 2nd acceptance

3rd acceptance possible

Non-sensitive period

CKIO

Bus cycle

DREQ

(Overrun 0,

high-level)

DACK

(High-active)

DREQ

(Overrun 1,

high-level)

DACK

(High-active)

CKIO

Bus cycle

Figure 13.21 Example of DREQ Input Detection in Cycle Steal Mode Level Detection

When DACK is Divided to 4 by Idle Cycles