Section 20 USB Function Module

Rev. 4.00 Sep. 14, 2005 Page 785 of 982

REJ09B0023-0400

20.7.2 DMA Transfer for Endpoint 2

When the transmitted data for EP2 is transferred by DMA when the data on one side of FIFO (64

bytes) becomes full an equivalent processing of writing 1 to the USBTRG/PKTE bit is

automatically performed in the module. Therefore, when data to be transferred is a multiple of 64

bytes, writing 1 to the USBTRG/PKTE bit is not necessary.

For the data less than 64 bytes, a 1 should be written to the USBTRG/PKTE bit by a DMA

transfer end interrupt of the DMAC. If a 1 is written to the USBTRG/PKTE bit for transferring the

maximum number of bytes (64 bytes), the correct operation cannot be guaranteed.

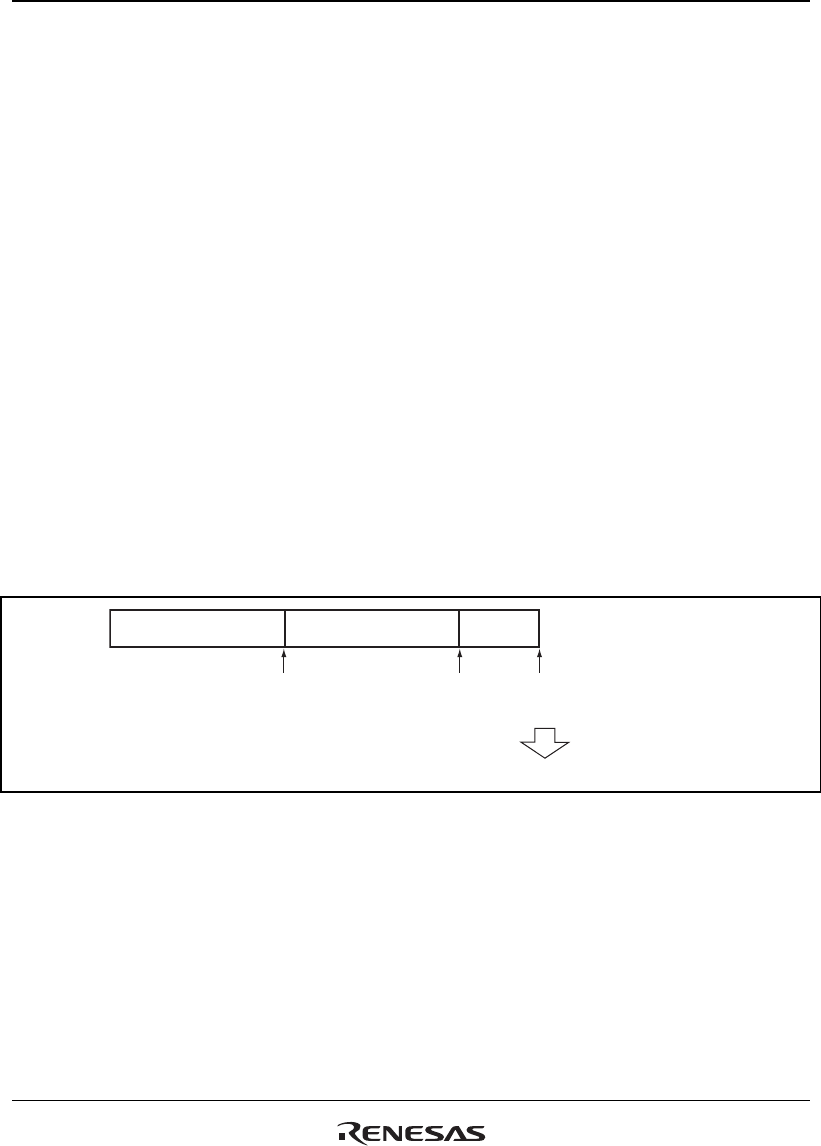

For example, if 150 bytes of data are transmitted to the host, the equivalent processing if writing 1

to the USBTRG/PKTE bit is automatically performed internally in the two places in figure 20.16.

This processing is done when the data on the currently selected FIFO becomes full meaning that

the processing is to be automatically performed only when 64 bytes of data are transferred.

When the last 22 bytes are transferred, write 1 to the USBTRG/PKTE bit because this is not

automatically written to. There is no data to be transferred in the application side, but this module

outputs the DMA transfer request for EP2 as long as the FIFO has a space. When all the data is

transferred by DMA, write 0 to the USBDMA/EP2DMAE bit to cancel the DMA transfer request

for EP2.

Generate DMA transfer end interrput

PKTE

(automatically written)

PKTE

(automatically written)

PKTE

(automatically written)

64 bytes 64 bytes

22 bytes

Figure 20.16 EP2 PKTE Operation