Section 18 Multi-Function Timer Pulse Unit (MTU)

Rev. 4.00 Sep. 14, 2005 Page 612 of 982

REJ09B0023-0400

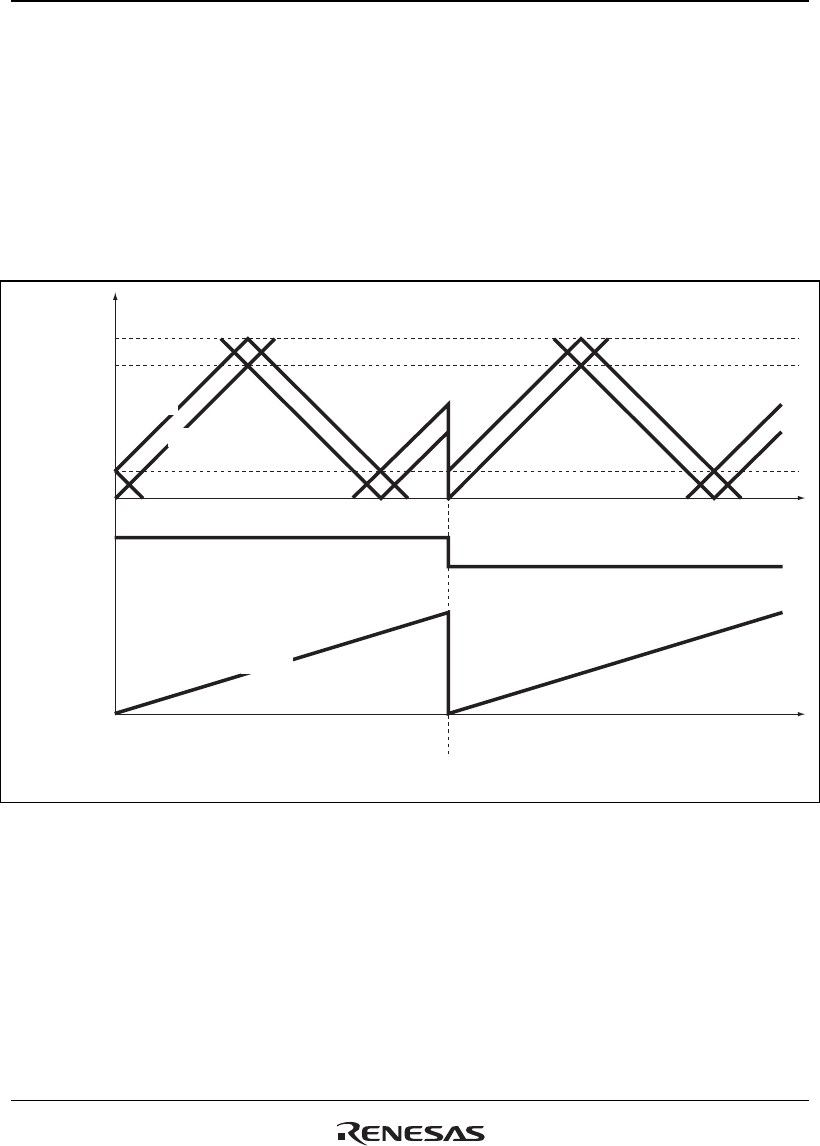

Counter Clearing by another Channel: In complementary PWM mode, by setting a mode for

synchronization with another channel by means of the timer synchro register (TSYR), and

selecting synchronous clearing with bits CCLR2 to CCLR0 in the timer control register (TCR), it

is possible to have TCNT_3, TCNT_4, and TCNTS cleared by another channel.

Figure 18.49 illustrates the operation.

Use of this function enables counter clearing and restarting to be performed by means of an

external signal.

TGRA_3

TCDR

TDDR

H'0000

Channel 1

Input capture A

TCNT_1

TCNT_3

TCNT_4

TCNTS

Synchronous counter clearing by channel 1 input capture A

Figure 18.49 Counter Clearing Synchronized with Another Channel