Section 1 Overview

Rev. 4.00 Sep. 14, 2005 Page 21 of 982

REJ09B0023-0400

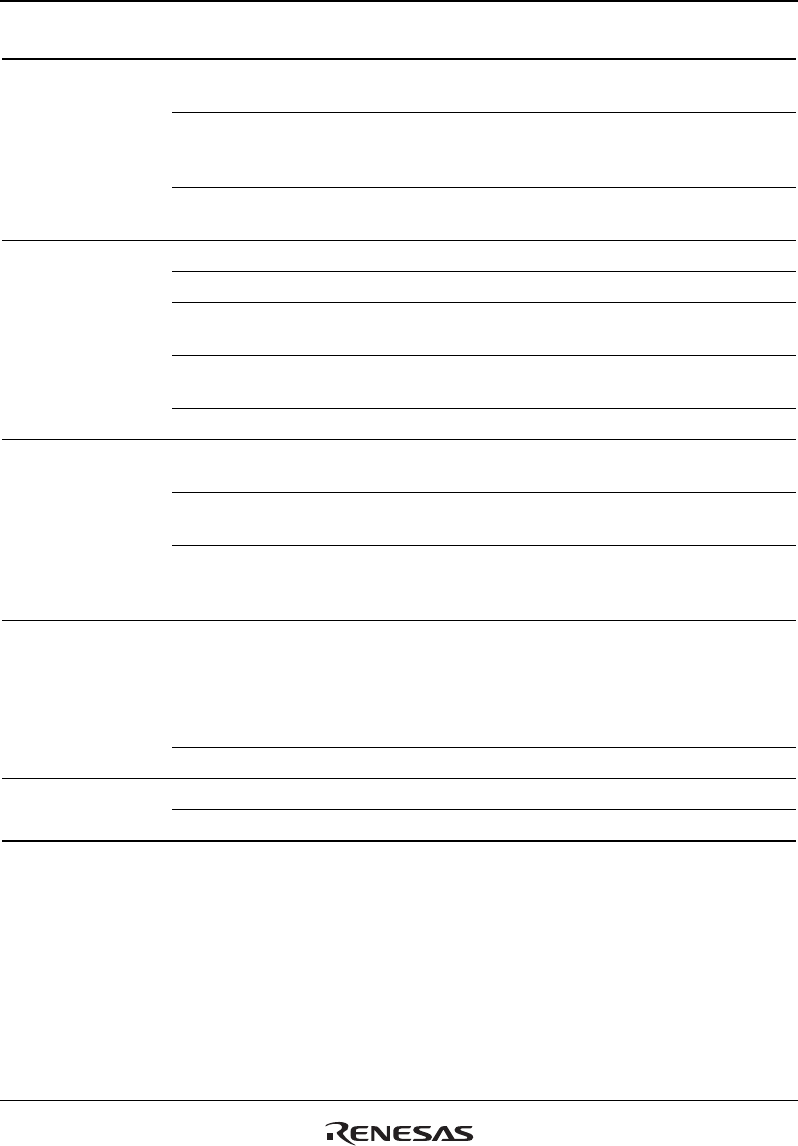

Classification Symbol I/O Name Function

DREQ0,

DREQ1

I DMA-transfer

request

Input pin for external requests for

DMA transfer.

DACK0,

DACK1

O DMA-transfer

request receive

Output pin for request receive, in

response to external requests for

DMA transfer.

Direct memory

access controller

(DMAC)

TEND0 O DMA-transfer end

output

Output pin for DMA transfer end

signal

TCK I Test clock Test-clock input pin.

TMS I Test mode select Inputs the test-mode select signal.

TDI I Test data input Serial input pin for instructions and

data.

TDO O Test data

output

Serial output pin for instructions and

data.

User debugging

interface

(H-UDI)

TRST I Test reset Initialization-signal input pin.

AUDATA3 to

AUDATA0

O AUD data Data output pins in AUD-trace mode.

AUDCK O AUD clock Sync-clock output pin in AUD-trace

mode.

Advanced user

debugger

(AUD)

AUDSYNC O AUD sync

signal

Data start-position acknowledge-

signal output pin in AIUD-trace

mode.

ASEBRKAK O Break mode

acknowledge

Indicates that the E10A emulator has

entered its break mode.

For the connection with the E10A,

see the SH7641 E10A Emulator

User's Manual (tentative title).

E10A interface

ASEMD0 I ASE mode Sets the ASE mode.

SCL I/O Serial clock pin Serial clock input/output pin I

2

C bus interface 2

SDA I/O Serial data pin Serial data input/output pin