Section 17 Compare Match Timer (CMT)

Rev. 4.00 Sep. 14, 2005 Page 513 of 982

REJ09B0023-0400

17.3 Operation

17.3.1 Interval Count Operation

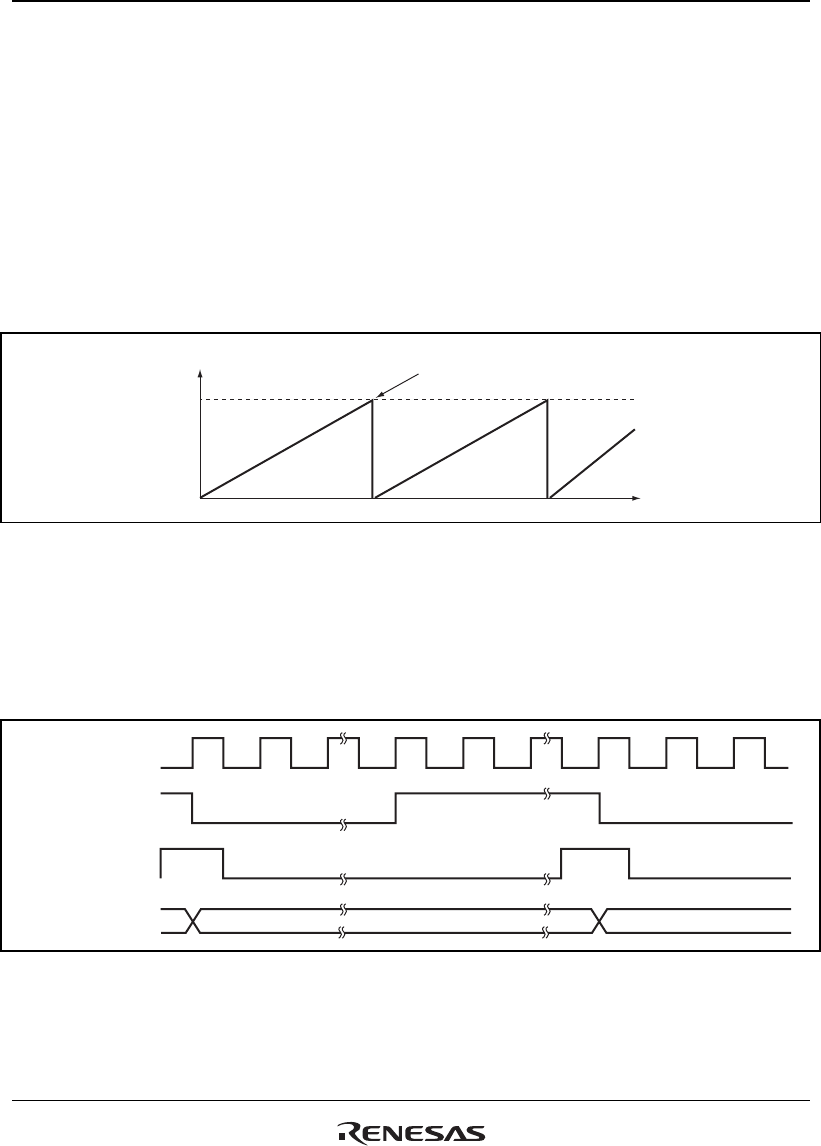

When an internal clock is selected with the CKS1 and CKS0 bits in CMCSR and the STR bit in

CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in

CMCNT and CMCOR match, CMCNT is cleared to H'0000 and the CMF flag in CMCSR is set to

1. CMCNT then starts counting up again from H'0000.

Figure 17.2 shows the operation of the compare match counter.

CMCOR

H'0000

CMCNT value

Time

Counter cleared by compare

match with CMCOR

Figure 17.2 Counter Operation

17.3.2 CMCNT Count Timing

One of four internal clocks (Pφ/4, Pφ/8, Pφ/16, and Pφ/64) obtained by dividing the Pφ clock can

be selected with bits CKS1 and CKS0 in CMCSR. Figure 17.3 shows the timing.

Peripheral operating

clock (Pφ)

Clock

N

Clock

N + 1

Internal clock

Count clock

CMCNT

N

N + 1

Figure 17.3 Count Timing