Section 14 U Memory

Rev. 4.00 Sep. 14, 2005 Page 452 of 982

REJ09B0023-0400

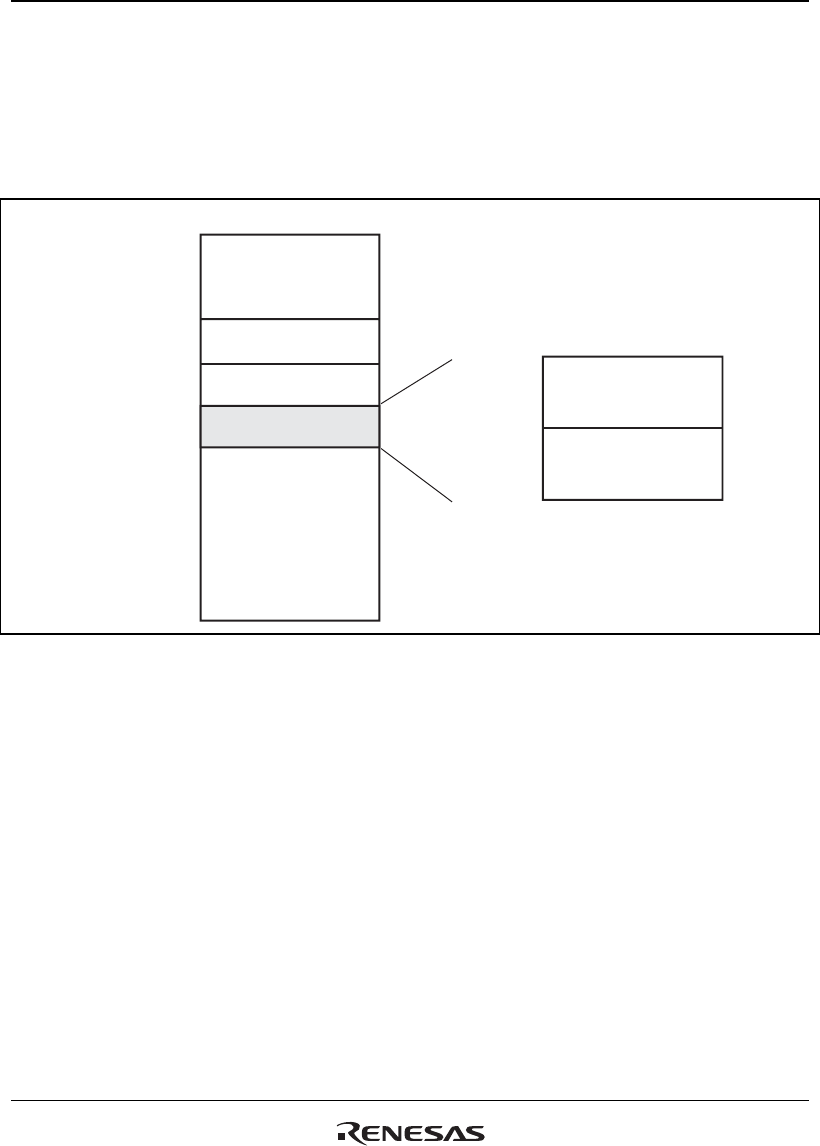

14.2 U Memory Access from CPU

The U memory can be accessed by the CPU from spaces P0 and P2. Access from the CPU is via

the I bus when U memory is space P0, and via the L bus when space P2. To use the L bus, one

cycle access is performed unless page conflict occurs. Using the I bus takes more than one cycle.

Area1, 64 Mbytes

U memory space

Address A[28:0]

Address A[28:0]

I/O space

16 Mbytes

X/Y memory

Reserved

Reserved

H'04000000

H'05000000

H'0501FFFF

H'055F0000

H'0560FFFF

H'05610000

H'07FFFFFF

U memory page1

64 kbytes

U memory page0

64 kbytes

H'0560FFFF

H'05600000

H'055FFFFF

H'055F0000

Figure 14.1 U Memory Address Mapping

14.3 U Memory Access from DSP

The DSP can access the U memory through spaces P0 and P2 using a single data transfer

instruction. Access from the DSP is via the I bus when the address is space P0, and via the L bus

when the address is space P2. To use the L bus, one cycle access is performed unless page conflict

occurs. Using the I bus takes more than one cycle.

14.4 U Memory Access from DMAC

The U memory also exists on the I bus and can be accessed by the DMAC. Use addresses

H'55F0000 to H'560FFFF.