Section 9 Exception Handling

Rev. 4.00 Sep. 14, 2005 Page 198 of 982

REJ09B0023-0400

9.1 Register Descriptions

There are three registers for exception handling. A register with an undefined initial value should

be initialized by the software.

• TRAPA exception register (TRA)

• Exception event register (EXPEVT)

• Interrupt event register 2 (INTEVT2)

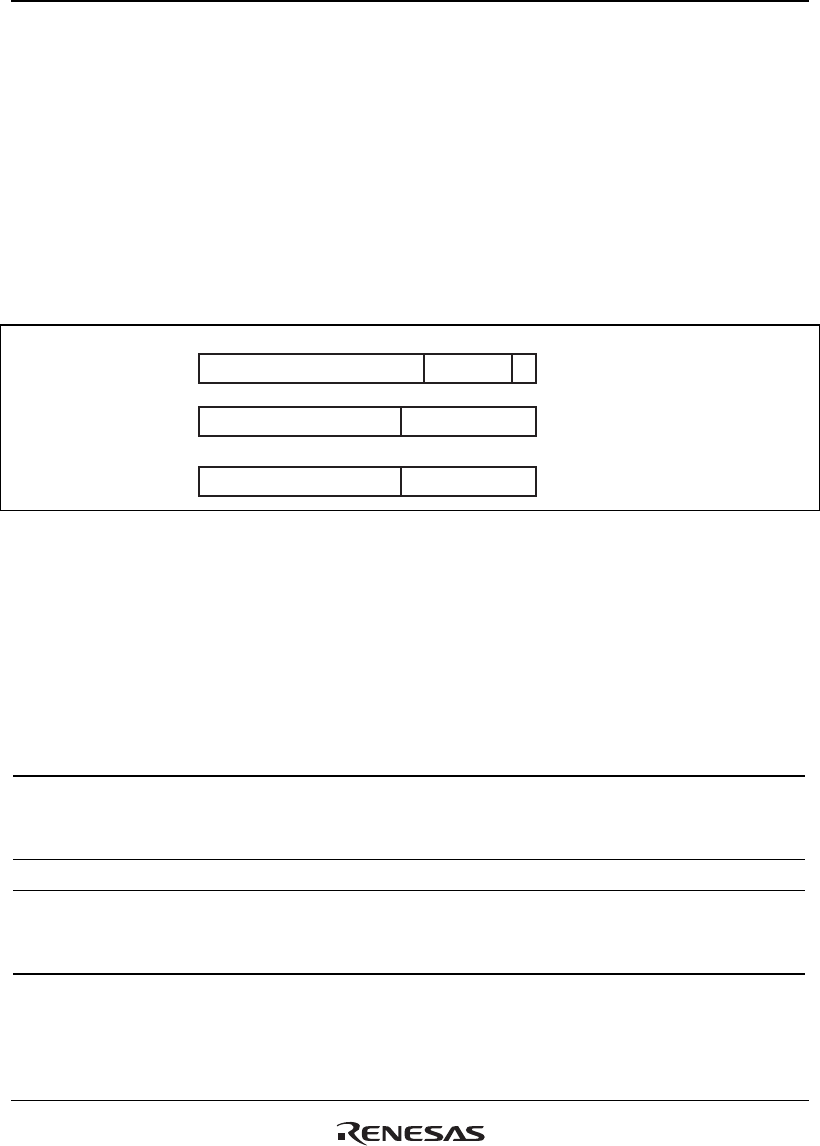

Figure 9.1 shows the bit configuration of each register.

31

TRA

EXPEVT

INTEVT2

TRA

EXPEVT

INTEVT2

10 9 2 1 0

31 12 11 0

0

0

0

0

31 12 11 0

Figure 9.1 Register Bit Configuration

9.1.1 TRAPA Exception Register (TRA)

TRA is assigned to address H'FFFFFFD0 and consists of the 8-bit immediate data (imm) of the

TRAPA instruction. TRA is automatically specified by the hardware when the TRAPA instruction

is executed. Only bits 9 to 2 of the TRA can be re-written using the software.

Bit Bit Name

Initial

Value R/W Description

31 to 10 R Reserved

These bits are always read as 0. The write value

should always be 0.

9 to 2 TRA R/W 8-Bit Immediate Data

1, 0 R Reserved

These bits are always read as 0. The write value

should always be 0.