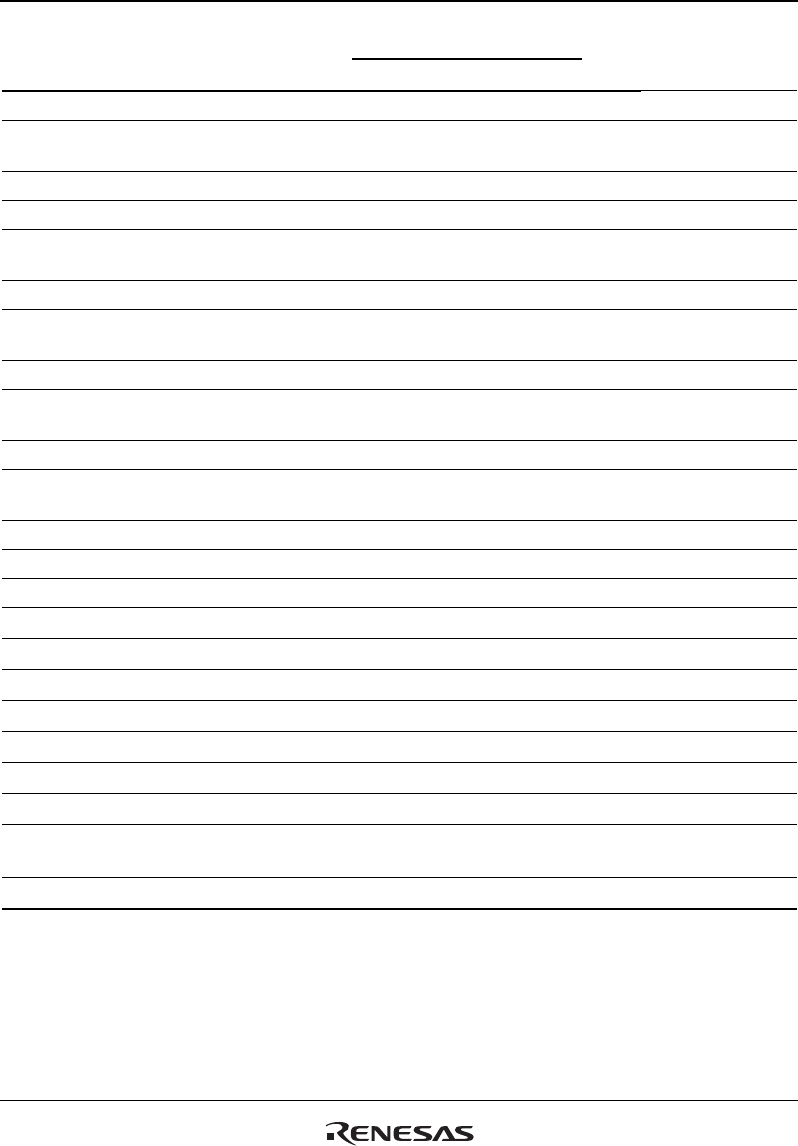

Section 25 Electrical Characteristics

Rev. 4.00 Sep. 14, 2005 Page 924 of 982

REJ09B0023-0400

Bφ = 50 MHz*

Item Symbol Min. Max. Unit Figure(s)

Write data delay time 1 t

WDD1

— 14 ns 25.13 to 25.21

Write data delay time 2 t

WDD2

— 14 ns 25.27 to 25.30,

25.34 to 25.36

Write data delay time 3 t

WDD3

— 1/2t

cyc

+ 14 ns 25.40

Write enable hold time 1 t

WDH1

1 — ns 25.13 to 25.21

Write enable hold time 2 t

WDH2

1 — ns 25.27 to 25.30,

25.34 to 25.36

Write enable hold time 3 t

WDH3

1/2t

cyc

— ns 25.40

WAIT setup time 1 t

WTS1

1/2t

cyc

+ 8 — ns 25.14, 25.15,

25.17 to 25.22

WAIT setup time 2 t

WTS2

8 — ns 25.16

WAIT hold time 1 t

WTH1

1/2t

cyc

+ 4 — ns 25.14, 25.15,

25.17 to 25.22

WAIT hold time 2 t

WTH2

4 — ns 25.16

RAS delay time 1 t

RASD1

1 12 ns 25.23 to 25.34,

25.36 to 25.39

RAS delay time 2 t

RASD2

1/2t

cyc

1/2t

cyc

+ 12 ns 25.40, 25.41

CAS delay time 1 t

CASD1

1 12 ns 25.23 to 25.39

CAS delay time 2 t

CASD2

1/2t

cyc

1/2t

cyc

+ 12 ns 25.40, 25.41

DQM delay time 1 t

DQMD1

1 12 ns 25.23 to 25.36

DQM delay time 2 t

DQMD2

1/2t

cyc

1/2t

cyc

+ 12 ns 25.40, 25.41

CKE delay time 1 t

CKED1

1 12 ns 25.38

CKE delay time 2 t

CKED2

1/2t

cyc

1/2t

cyc

+ 12 ns 25.41

AH delay time t

AHD

1/2t

cyc

1/2t

cyc

+ 12 ns 25.18

Multiplexed address delay time t

MAD

— 12 ns 25.18

Multiplexed address hold time t

MAH

0 — ns 25.18

DACK, TEND delay time t

DACD

— Refer to

peripheral modules

ns 25.13 to 25.34

FRAME delay time t

FMD

1 12 ns 25.19

Note: * The maximum value (f

max

) of Bφ (external bus clock) depends on the number of wait

cycles and the system configuration of your board.