Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 337 of 982

REJ09B0023-0400

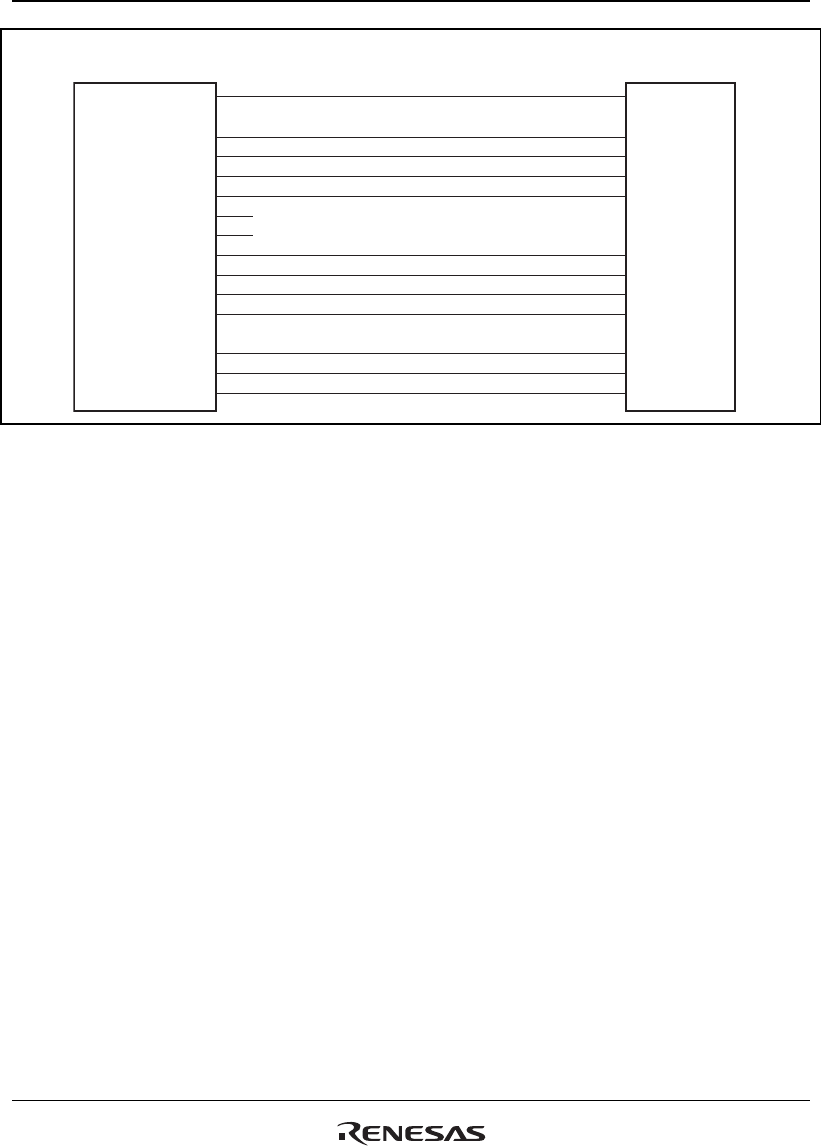

A14

A1

CKE

CKIO

CSn

RASU

CASU

RASL

CASL

RD/WR

D15

D0

DQMLU

DQMLL

64M SDRAM

(1M

× 16-bit × 4-bank)

. . .

A13

A0

CKE

CLK

CS

RAS

CAS

WE

I/O15

I/O0

DQMU

DQML

. . .

. . .

. . .

This LSI

Unused

Unused

Figure 12.16 Example of 16-Bit Data Width SDRAM Connection

(RASU and CASU are Not Used)