Section 3 DSP Operation

Rev. 4.00 Sep. 14, 2005 Page 120 of 982

REJ09B0023-0400

Note: Data transfer by an LDS or STS instruction is possible since DSR is defined as a system

register.

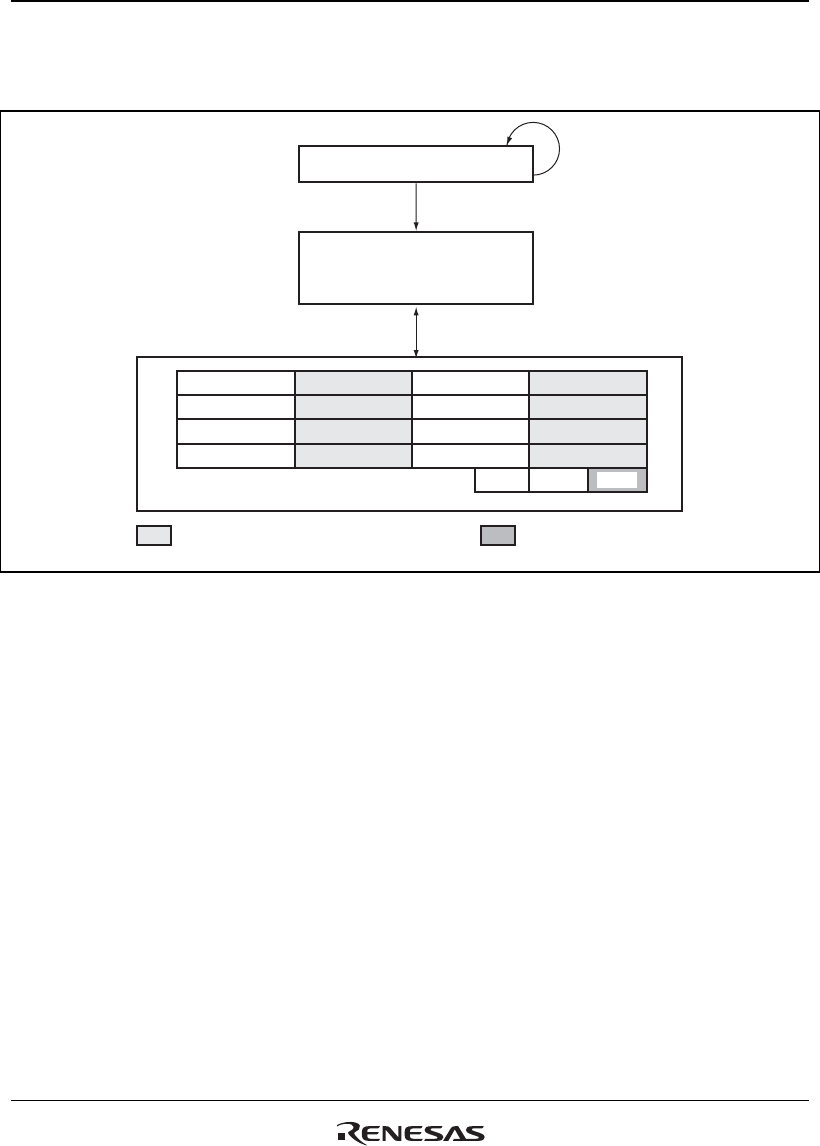

LAB [31:0]

LDB [15:0]

–2, 0, +2, +R8

Pointer (R2, R3, R4, R5)

Any memory areas

Not affected for store and cleared for load

See description of A0G and A1G.

Cannot be specified

X0

X1

Y0

Y1

M0

M1

DSR

A0G A1G

A0

A1

Figure 3.15 Single Data-Transfer Operation Flow (Word)