Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 43 of 982

REJ09B0023-0400

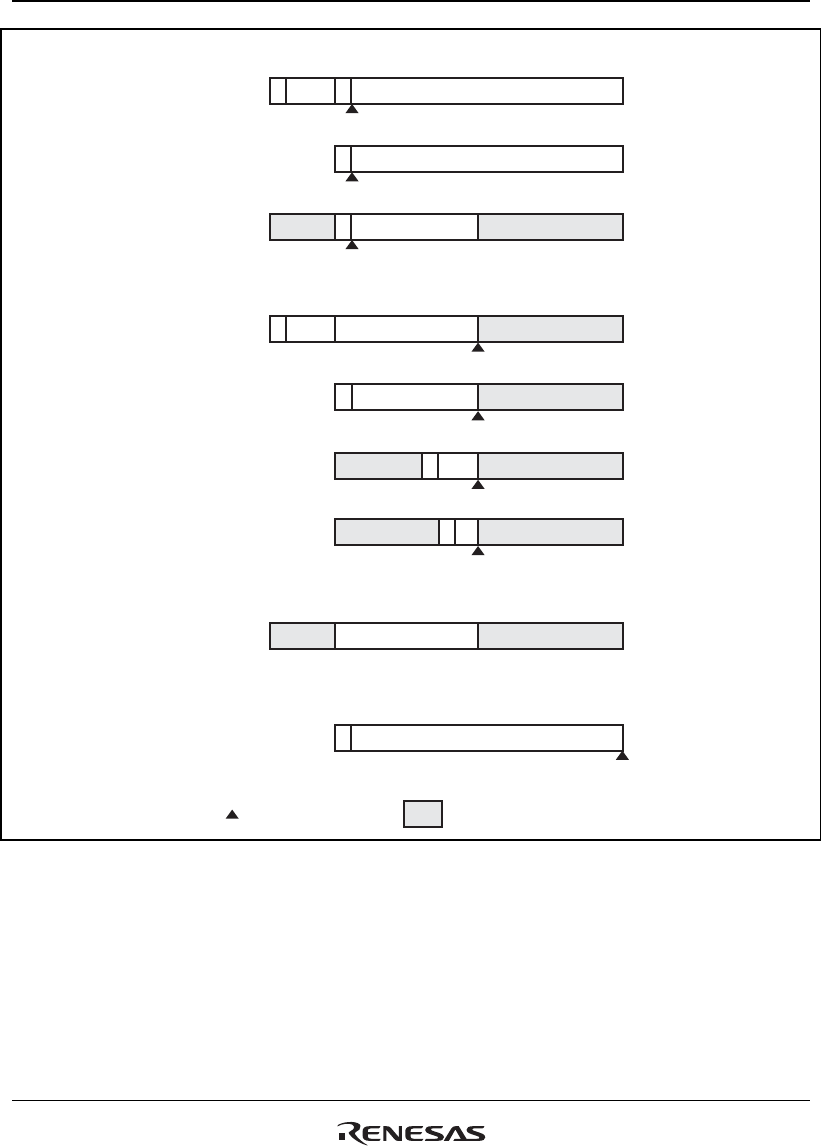

39

S

31 30 0

–2

8

to +2

8

– 2

–31

39

S

32 31 0

–2

23

to +2

23

– 1

39

S

S

31 30 16 15

16 15

0

–1 to +1 – 2

–15

39 31 16 15 0

S

31 0

–2

15

to +2

15

– 1

16

15

31 22 0

–32 to +32

16

15

S

31 21 0

–16 to +16

16

15

S

31 30 0

–1 to +1 – 2

–31

S

31 0

–2

31

to +2

31

– 1

DSP type fixed point

DSP type integer

DSP type logical

With guard bits

CPU type integer

S: Sign bit

Longword

: Binary point : Does not affect the operations

Without guard bits

With guard bits

Without guard bits

Multiplier input

Shift amount for

arithmetic shift (PSHA)

Shift amount for

logical shift (PSHL)

Figure 2.10 Data Formats

The shift amount for the arithmetic shift (PSHA) instruction has a 7-bit field that can represent

values from –64 to +63, but –32 to +32 are valid numbers for the instruction. Also the shift

amount for a logical shift operation has a 6-bit field, but –16 to +16 are valid numbers for the

instruction.