Section 13 Direct Memory Access Controller (DMAC)

Rev. 4.00 Sep. 14, 2005 Page 425 of 982

REJ09B0023-0400

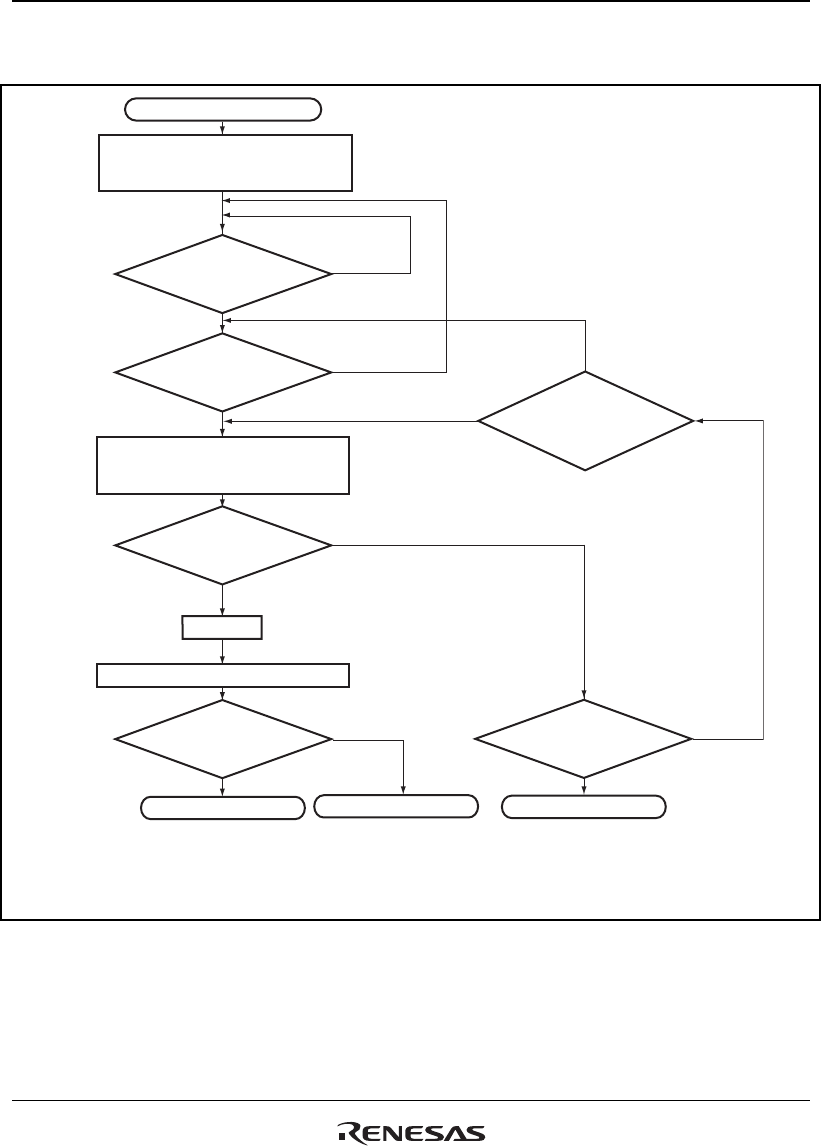

Figure 13.2 is a flowchart of this procedure.

Normal end

NMIF = 1

or AE = 1 or DE = 0

or DME = 0?

Bus mode,

transfer request mode,

DREQ detection selection

system

Initial settings

(SAR, DAR, DMATCR, CHCR,

DMAOR, DMARS)

Transfer (1 transfer unit);

DMATCR – 1 → DMATCR, SAR and

DAR updated

DEI interrupt request (when IE = 1)

TE = 1

No

Yes

No

Yes

No

Yes

Yes

No

Yes

No

*

3

*

2

Start

Transfer aborted

DMATCR = 0?

Transfer request

occurs?*

1

DE, DME = 1 and

NMIF, AE, TE = 0?

NMIF = 1

or AE = 1 or DE = 0

or DME = 0?

Transfer end

Notes: 1. In auto-request mode, transfer begins when NMIF and TE are all 0 and the DE and DME bits are

set to 1.

2. DREQ = level detection in burst mode (external request) or cycle-steal mode.

3. DREQ = edge detection in burst mode (external request), or auto-request mode in burst mode.

Figure 13.2 DMA Transfer Flowchart