Section 7 Cache

Rev. 4.00 Sep. 14, 2005 Page 181 of 982

REJ09B0023-0400

Data Array: Holds a 16-byte instruction or data. Entries are registered in the cache in line units

(16 bytes). The data array is not initialized by a power-on or manual reset, standby mode, module

standby mode, and sleep mode.

LRU: With the 4-way set associative system, up to four instructions or data with the same entry

address (address bits 11 to 4) can be registered in the cache. When an entry is registered, LRU

shows which of the four ways it is recorded in. There are six LRU bits, controlled by hardware. A

least-recently-used (LRU) algorithm is used to select the way that has been least recently accessed.

Six LRU bits indicate the way to be replaced in case of a cache miss.

The relationship between LRU and way replacement is shown is table 7.3 when the cache lock

function is not used 1 concerning the case where the cache lock function is used, see section 7.2.2,

Cache Control Register 2 (CCR2). If a bit pattern other than those listed in table 7.3 is set in the

LRU bits by software, the cache will not function correctly. When modifying the LRU bits by

software, set one of the patterns listed in table 7.3.

The LRU bits are initialized to 000000 by a power-on reset and retaining the previous value by a

manual reset, standby mode, module standby mode, and sleep mode.

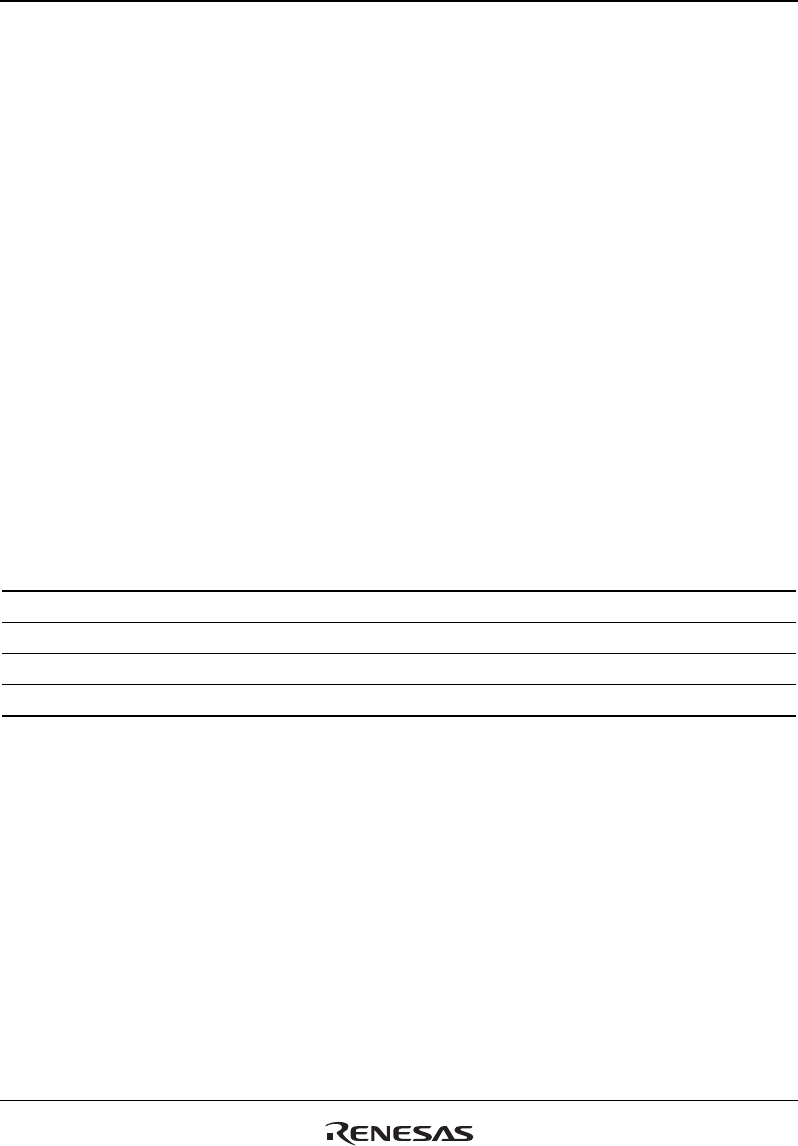

Table 7.3 LRU and Way Replacement

LRU (Bits 5 to 0) Way to be Replaced

000000, 000100, 010100, 100000, 110000, 110100 3

000001, 000011, 001011, 100001, 101001, 101011 2

000110, 000111, 001111, 010110, 011110, 011111 1

111000, 111001, 111011, 111100, 111110, 111111 0