Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 271 of 982

REJ09B0023-0400

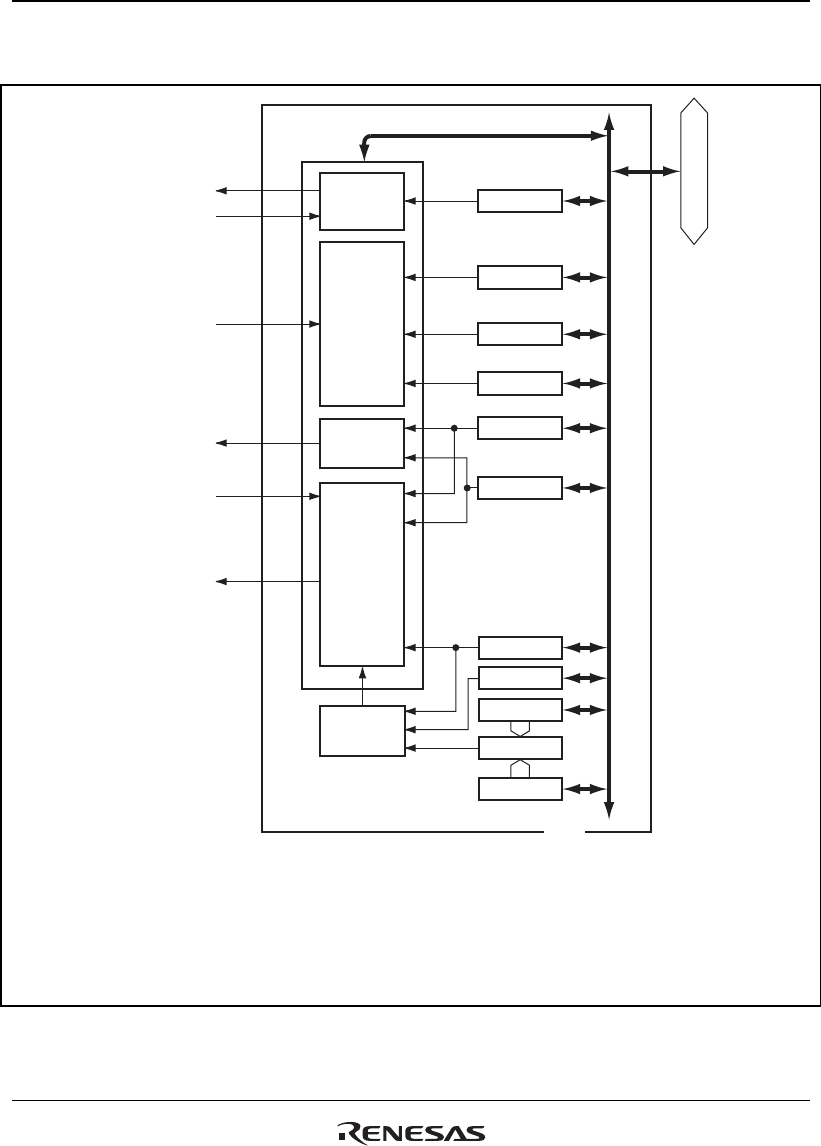

BSC functional block diagram is shown in figure 12.1.

CMNCR

CS0WCR

CS6BWCR

RWTCNT

CS0BCR

CS6BBCR

SDCR

RTCSR

RTCNT

RTCOR

Comparator

Bus

mastership

controller

Wait

controller

Area

controller

Internal bus

Memory

controller

Refresh

controller

[Legend]

Module bus

BSC

CS0, CS2, CS3,

CS4, CS5A, CS5B,

CS6A, CS6B

WAIT

MD3

A25 to A0,

D31 to D0

BACK

BREQ

BS, RD/WR,

RD, WE3 to WE0,

RASU, RASL,

CASU, CASL

CKE, DQMxx, AH,

FRAME

CMNCR:

CSnWCR:

RWTCNT:

CSnBCR:

SDCR:

RTCSR:

RTCNT:

RTCOR:

Common control register

CSn space wait control register (n = 0, 2, 3, 4, 5A, 5B, 6A, 6B)

Reset wait counter

CSn space bus control register (n = 0, 2, 3, 4, 5A, 5B, 6A, 6B)

SDRAM control register

Refresh timer control/status register

Refresh timer counter

Refresh time constant register

. .

.

. . .

. . .

. . .

. .

.

Figure 12.1 BSC Functional Block Diagram