Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 330 of 982

REJ09B0023-0400

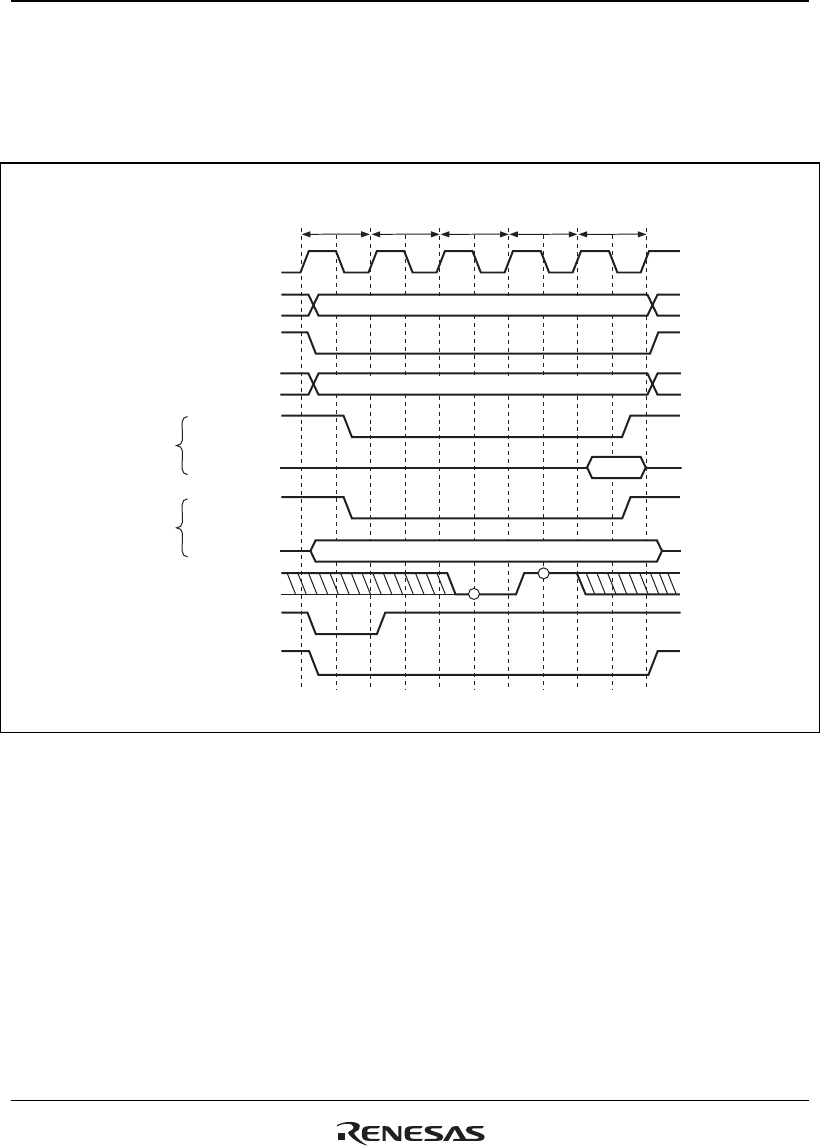

When the WM bit in CSnWCR is cleared to 0, the external wait input WAIT signal is also

sampled. WAIT pin sampling is shown in figure 12.10. A 2-cycle wait is specified as a software

wait. The WAIT signal is sampled on the falling edge of CKIO at the transition from the T1 or Tw

cycle to the T2 cycle.

T1

CKIO

A25 to A0

CSn

RD/WR

RD

D31 to D0

WEn

D31 to D0

WAIT

Tw Tw

Twx T2

Read

Write

BS

Wait states inserted

by WAIT signal

DACKn*

Note: * The waveform for DACKn is when active low is specified.

Figure 12.10 Wait State Timing for Normal Space Access

(Wait State Insertion Using WAIT Signal)