Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 66 of 982

REJ09B0023-0400

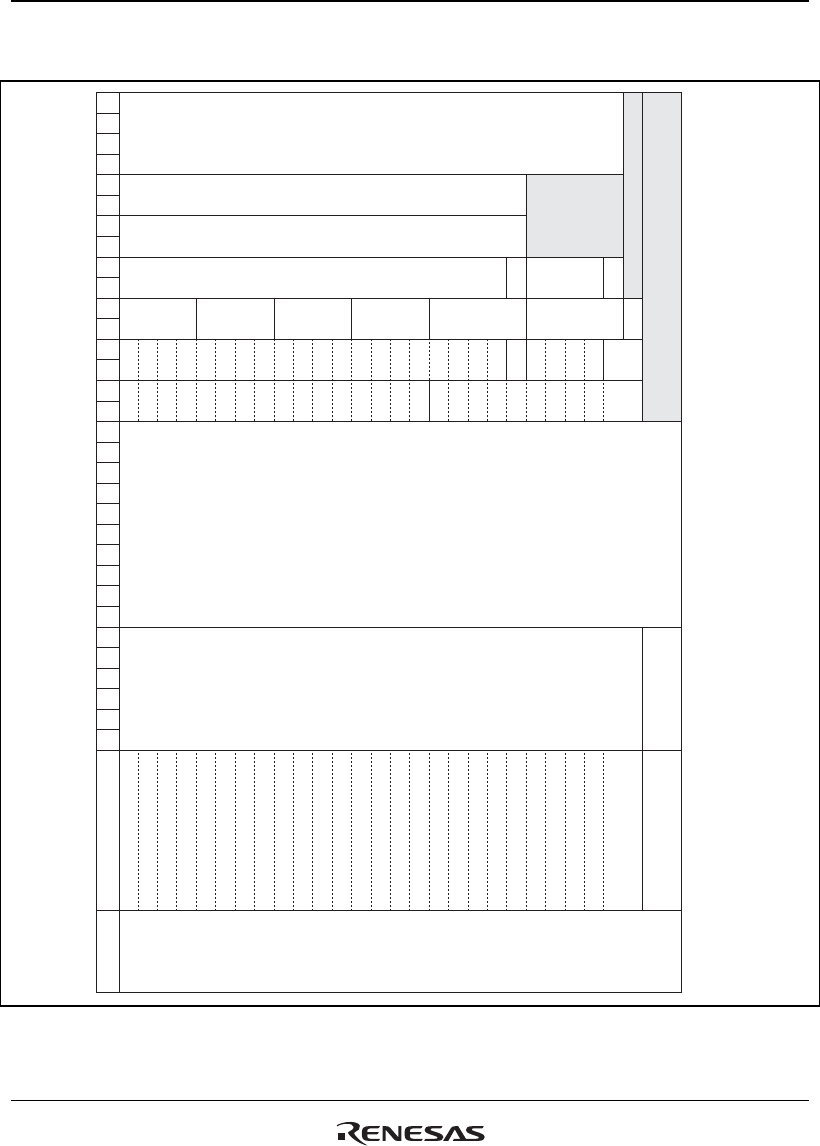

Table 2.17 B-Field ALU Operation Instructions and Multiply Instructions (2)

[if cc] PSHL Sx, Sy, Dz

[if cc] PSHA Sx, Sy, Dz

[if cc] PSUB Sx, Sy, Dz

[if cc] PADD Sx, Sy, Dz

Reserved

[if cc] PAND Sx, Sy, Dz

[if cc] PXOR Sx, Sy, Dz

[if cc] POR Sx, Sy, Dz

[if cc] PDEC Sx, Dz

[if cc] PINC Sx, Dz

[if cc] PDEC Sy, Dz

[if cc] PINC Sy, Dz

[if cc] PCLR Dz

[if cc] PDMSB Sx, Dz

Reserved

[if cc] PDMSB Sy, Dz

[if cc] PNEG Sx, Dz

[if cc] PCOPY Sx, Dz

[if cc] PNEG Sy, Dz

[if cc] PCOPY Sy, Dz

Reserved

[if cc] PSTS MACH, Dz

[if cc] PSTS MACL, Dz

[if cc] PLDS Dz, MACH

[if cc] PLDS Dz, MACL

(*

2

) Reserved

Reserved

MnemonicType

if cc

01:

10:

DCT

11:

DCF

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14

13 12 11 10 9 8 7 6 543 2 1 0

Conditional

3-operand

instructions

111110

11

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Sx

0:X0

1:X1

2:A0

3:A1

0

0

1

1

1

1

0

0

1

0

1

0

1

*

0:(*

1

)

1:(*

1

)

2:(*

1

)

3:(*

1

)

4:(*

1

)

5:A1

6:(*

1

)

7:A0

8:X0

9:X1

A:Y0

B:Y1

C:M0

D:(*

1

)

E:M1

F:(*

1

)

Dz

111111

0

0

0

0

Sy

0:Y0

1:Y1

2:M0

3:M1

Uncon-

ditional

if cc

Notes: 1. Codes reserved for system use.

2. [if cc]: DCT (DC bit True), DCF (DC bit False) or none (unconditional instruction)

A field