Section 15 User Debugging Interface (H-UDI)

Rev. 4.00 Sep. 14, 2005 Page 459 of 982

REJ09B0023-0400

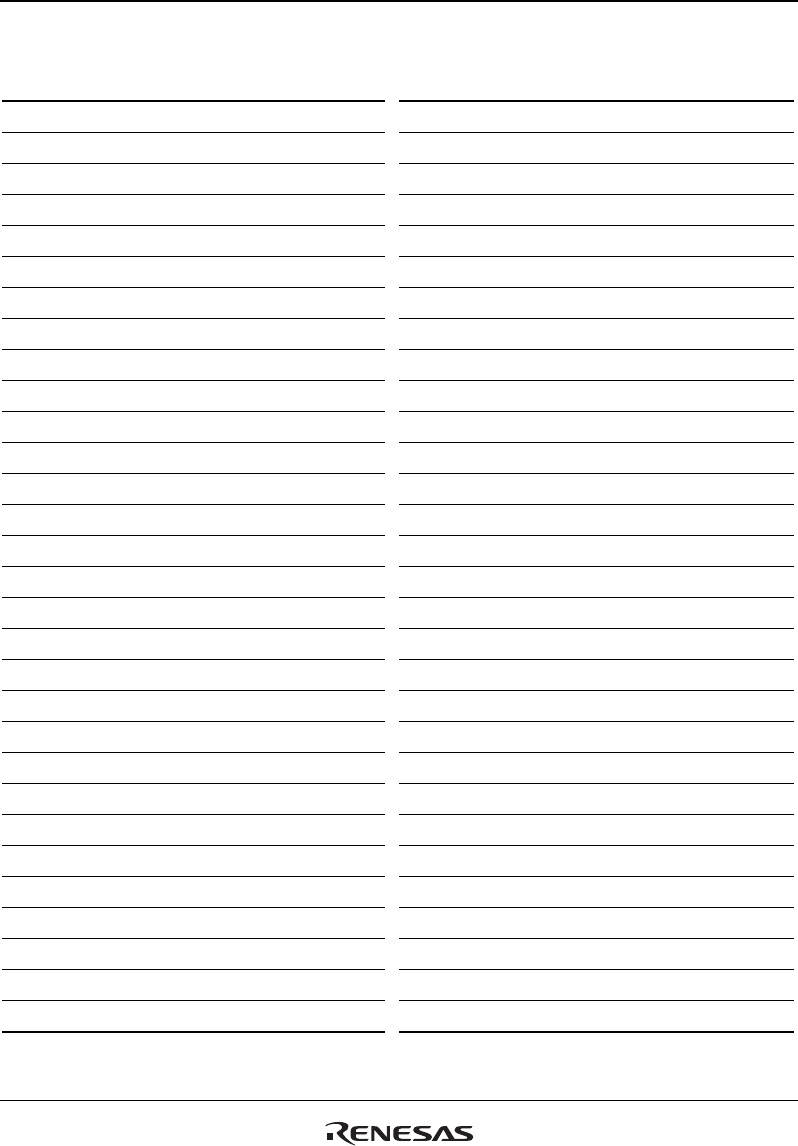

Table 15.3 This LSI Pins and Boundary Scan Register Bits

Bit Pin Name I/O Bit Pin Name I/O

From TDI 454 AUDATA3/PTJ11 IN

483 D7 IN 453 AUDSYNC/PTJ12 IN

482 D6 IN 452 NMI IN

481 D5 IN 451 IRQ0/PTJ0 IN

480 D4 IN 450 IRQ1/PTJ1 IN

479 D3 IN 449 IRQ2/PTJ2 IN

478 D2 IN 448 IRQ3/PTJ3 IN

477 D1 IN 447 IRQ4/PTJ4 IN

476 D0 IN 446 IRQ5/PTJ5 IN

475 CS3/PTA3 IN 445 IRQ6/PTJ6 IN

474 CS2/PTA2 IN 444 IRQ7/PTJ7 IN

473 UCLK/PTB0 IN 443 SCK0/PTH0 IN

472 VBUS/PTB1 IN 442 D7 OUT

471 SUSPND/PTB2 IN 441 D6 OUT

470 XVDATA/PTB3 IN 440 D5 OUT

469 TXENL/PTB4 IN 439 D4 OUT

468 TXDMNS/PTB5 IN 438 D3 OUT

467 TXDPLS/PTB6 IN 437 D2 OUT

466 DMNS/PTB7 IN 436 D1 OUT

465 DPLS/PTB8 IN 435 D0 OUT

464 A19/PTA8 IN 434 CS3/PTA3 OUT

463 A20/PTA9 IN 433 CS2/PTA2 OUT

462 A21/PTA10 IN 432 UCLK/PTB0 OUT

461 A22/PTA11 IN 431 VBUS/PTB1 OUT

460 A23/PTA12 IN 430 SUSPND/PTB2 OUT

459 A24/PTA13 IN 429 XVDATA/PTB3 OUT

458 A25/PTA14 IN 428 TXENL/PTB4 OUT

457 AUDATA0/PTJ8 IN 427 TXDMNS/PTB5 OUT

456 AUDATA1/PTJ9 IN 426 TXDPLS/PTB6 OUT

455 AUDATA2/PTJ10 IN 425 DMNS/PTB7 OUT