Section 3 DSP Operation

Rev. 4.00 Sep. 14, 2005 Page 126 of 982

REJ09B0023-0400

5. If a repeat loop has four or more instructions in it, any branch instructions (BRA, BSR, BT,

BF, BT/S, BF/S, BSRF, RTS, BRAF, RTE, JSR and JMP), repeat control instructions

(SETRC, LDRS and LDRE), load instructions for SR, RS, RE, and the TRAPA instruction

must not be written within the last three instructions from the bottom of a repeat loop. If

written, a general invalid instruction exception handling starts, and a certain address value

shown in table 3.16 is stored into SPC. In cases of repeat control instructions (SETRC, LDRS

and LDRE) and load instructions for SR, RS, and RE, and the TRAPA instruction they cannot

be placed in any other location of the repeat loop, either. If they are, the operation is not

guaranteed.

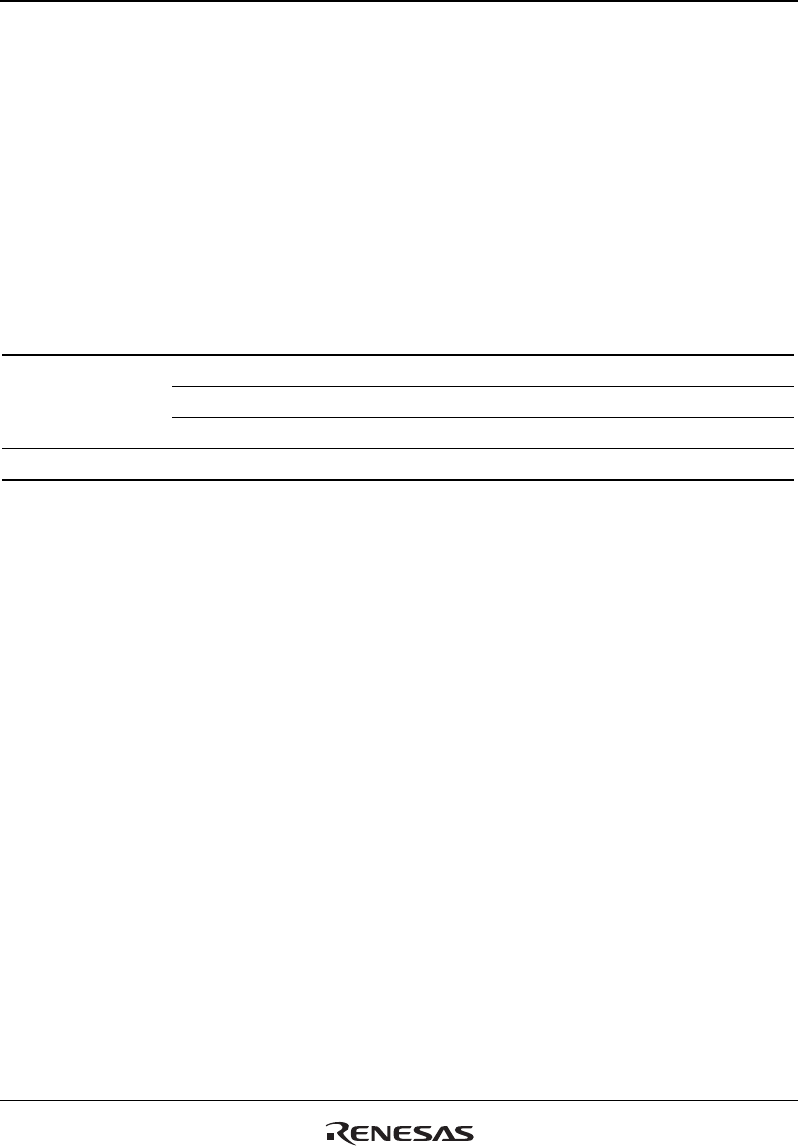

Table 3.16 Address Value to be Stored into SPC (2)

Condition Location Address to be Pushed

RC ≥ 2 instr3 Address of the illegal instruction

instr4 RptStart − 4

instr5 RptStart − 2

RC = 1 Any Address of the illegal instruction

6. If a repeat loop has less than four instructions in it, any PC relative instructions (MOVA

@(disp, PC),R0, etc.) don't work properly except for the instruction at the repeat top (instr1).

7. If a repeat loop has four or more instructions in it, any PC relative instructions (MOVA

@(disp, PC),R0, etc.) don't work properly at two instructions from the bottom of the repeat

loop.

8. The CPU has no repeat enable flag, however it uses the condition RC = 0 to disable repeat

control. Whenever the RC is not 0 and PC matches RE, the repeat control is alive. When 0 is

set in the RC, the repeat control is disabled but the repeat loop is executed once and does not

return to the repeat start as well as in the RC = 1 case. When RC = 1, the repeat loop is

executed once and does not return to the repeat start but the RC becomes 0 after completing

the execution of the repeat loop.

9. If a repeat loop has four or more instructions in it, any branch instructions, including

subroutine call and return instructions, cannot specify the instruction from inst3 to inst5 in the

previous example as the branch target address. If executed, the repeat control doesn't work, so

the program goes to the following instruction and the RC is not updated. When a repeat loop

has less than four instructions in it, the repeat control doesn't work properly and the RC value

in SR is not updated if the branch target is RptStart or a subsequent address.

10. Exception acceptance is restricted during repeat loop processing. See figure 3.18 for details on

restrictions.