Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 80 of 982

REJ09B0023-0400

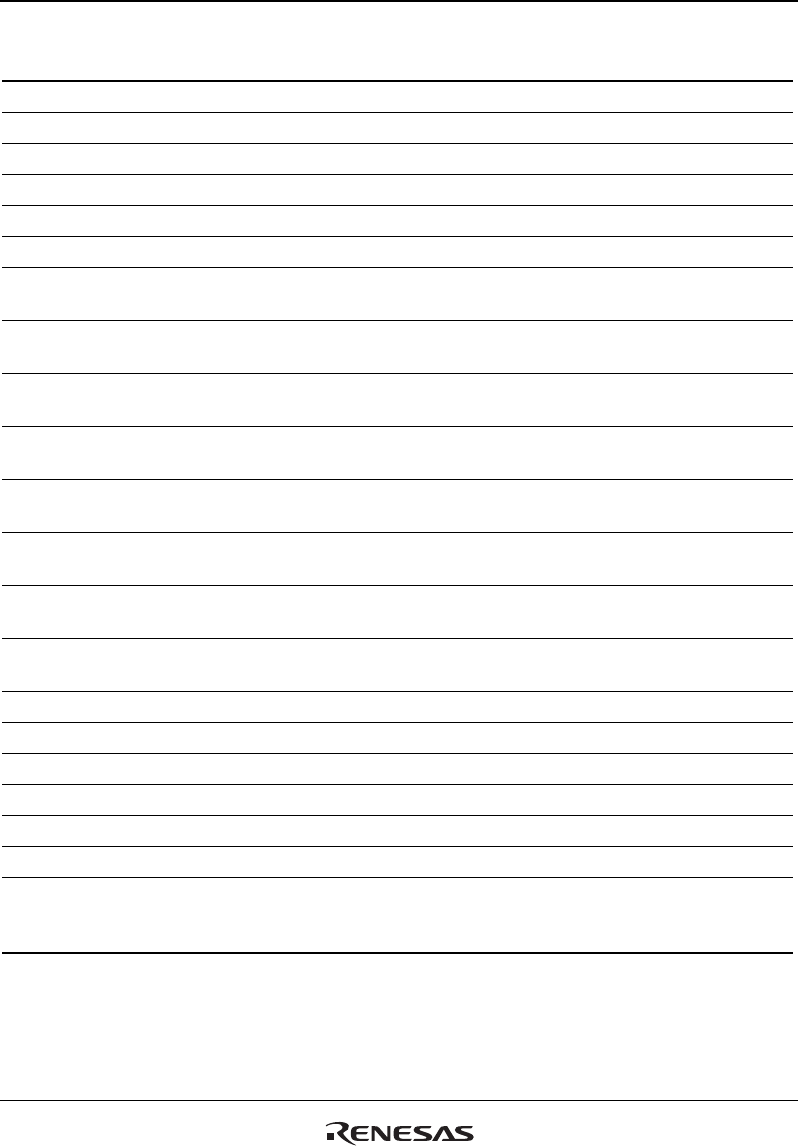

Instruction

Instruction Code

Operation

Execution

States

T Bit

STC R7_BANK,Rn 0000nnnn11110010 R7_BANK→ Rn 1 —

STC.L SR,@–Rn 0100nnnn00000011 Rn–4 → Rn, SR → (Rn) 1 —

STC.L GBR,@–Rn 0100nnnn00010011 Rn–4 → Rn, GBR → (Rn) 1 —

STC.L VBR,@–Rn 0100nnnn00100011 Rn–4 → Rn, VBR → (Rn) 1 —

STC.L SSR,@–Rn 0100nnnn00110011 Rn–4 → Rn, SSR → (Rn) 1 —

STC.L SPC,@–Rn 0100nnnn01000011 Rn–4 → Rn, SPC → (Rn) 1 —

STC.L R0_BANK,

@–Rn

0100nnnn10000011 Rn–4 → Rn, R0_BANK → (Rn) 1 —

STC.L R1_BANK,

@–Rn

0100nnnn10010011 Rn–4 → Rn, R1_BANK → (Rn) 1 —

STC.L R2_BANK,

@–Rn

0100nnnn10100011 Rn–4 → Rn, R2_BANK → (Rn) 1 —

STC.L R3_BANK,

@–Rn

0100nnnn10110011 Rn–4 → Rn, R3_BANK → (Rn) 1 —

STC.L R4_BANK,

@–Rn

0100nnnn11000011 Rn–4 → Rn, R4_BANK → (Rn) 1 —

STC.L R5_BANK,

@–Rn

0100nnnn11010011 Rn–4 → Rn, R5_BANK → (Rn) 1 —

STC.L R6_BANK,

@–Rn

0100nnnn11100011 Rn–4 → Rn, R6_BANK → (Rn) 1 —

STC.L R7_BANK,

@–Rn

0100nnnn11110011 Rn–4 → Rn, R7_BANK → (Rn) 1 —

STS MACH,Rn 0000nnnn00001010 MACH → Rn 1 —

STS MACL,Rn 0000nnnn00011010 MACL → Rn 1 —

STS PR,Rn 0000nnnn00101010 PR → Rn 1 —

STS.L MACH,@–Rn 0100nnnn00000010 Rn–4 → Rn, MACH → (Rn) 1 —

STS.L MACL,@–Rn 0100nnnn00010010 Rn–4 → Rn, MACL → (Rn) 1 —

STS.L PR,@–Rn 0100nnnn00100010 Rn–4 → Rn, PR → (Rn) 1 —

TRAPA #imm 11000011iiiiiiii PC → SPC, SR → SSR,

imm << 2 → TRA,

VBR + H'0100 → PC

8 —

Note: * Number of states before the chip enters the sleep state.

The table shows the minimum number of clocks required for execution. In practice, the

number of execution cycles will be increased if there is contention between an

instruction fetch and a data access, or if the destination register of a load instruction

(memory → register) is also used by the following instruction.