Section 11 User Break Controller (UBC)

Rev. 4.00 Sep. 14, 2005 Page 242 of 982

REJ09B0023-0400

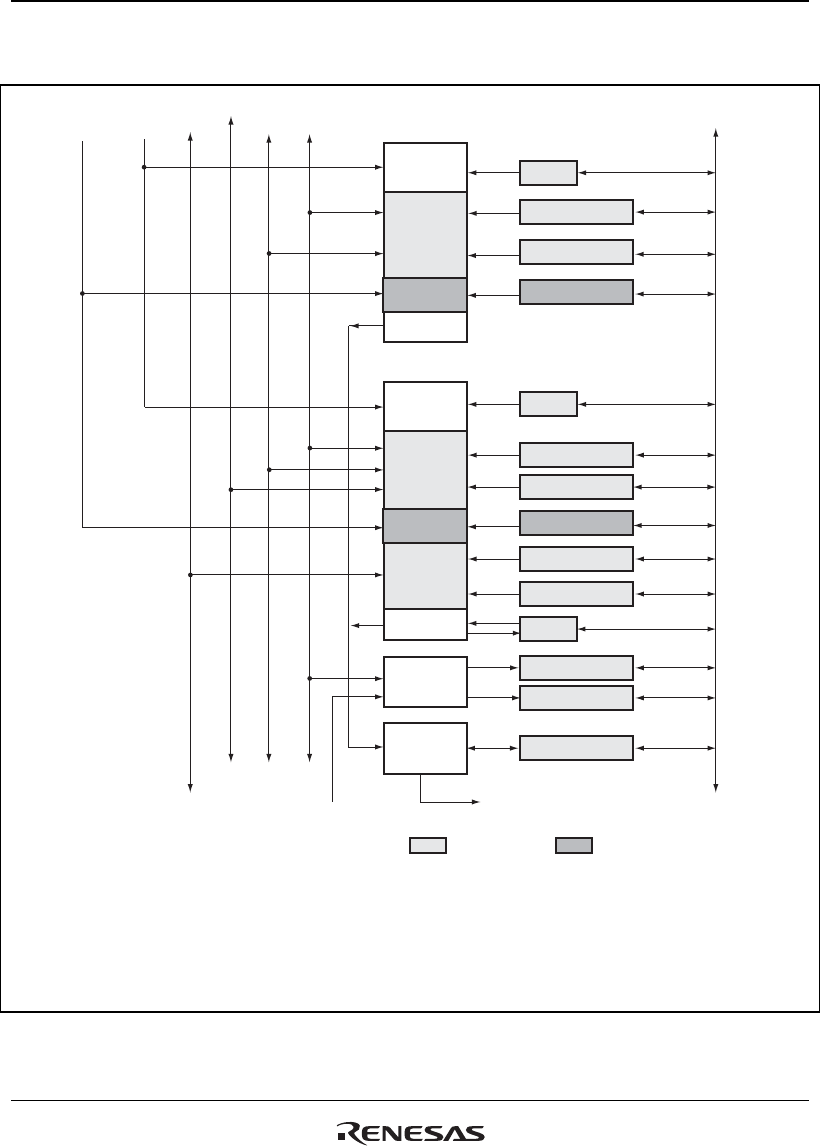

Figure 11.1 shows a block diagram of the UBC.

BBRA

BARA

BAMRA

CPU state

signals

XAB/YAB

IAB LAB

Internal bus

Access

comparator

Address

comparator

Channel A

Access

comparator

Address

comparator

Data

comparator

PC trace

CONTROL

Channel B

BBRB

BETR

BASRA

BASRB

BARB

BAMRB

BBRB

BDMRB

BRSR

BRDR

BRCR

User break request

UBC Location

CCN Location

LDB/IDB/

XDB/YDB

[Legend]

BBRA:

BARA:

BAMRA:

BASRA:

BBRB:

BARB:

BAMRB:

BASRB:

BDRB:

BDMRB:

BETR:

BRSR:

BRDR:

BRCR:

Break bus cycle register A

Break address register A

Break address mask register A

Break ASID register A

Break bus cycle register B

Break address register B

Break address mask register B

Break ASID register B

Break data register B

Break data mask register B

Break execution times register

Branch source register

Branch destination register

Break control register

Access

Control

ASID

comparator

ASID

comparator

ASID

Figure 11.1 Block Diagram of User Break Controller