Section 15 User Debugging Interface (H-UDI)

Rev. 4.00 Sep. 14, 2005 Page 470 of 982

REJ09B0023-0400

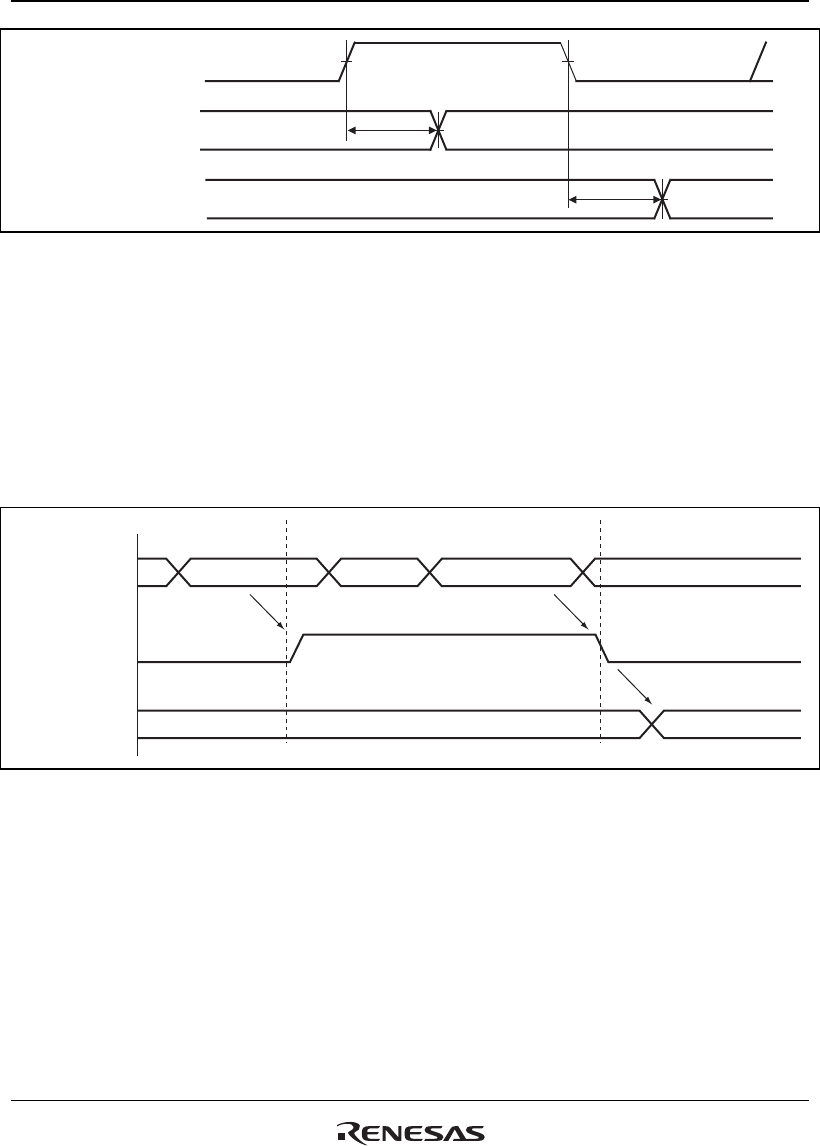

TDO

(when the H-UDI

command is set)

TCK

TDO

(when the boundary scan

command is set)

t

TDOD

t

TDOD

Figure 15.3 H-UDI Data Transfer Timing

15.4.4 H-UDI Reset

An H-UDI reset is executed by inputting an H-UDI reset assert command in SDIR. An H-UDI

reset is of the same kind as a power-on reset. An H-UDI reset is released by inputting an H-UDI

reset negate command. The required time between the H-UDI reset assert command and H-UDI

reset negate command is the same as time for keeping the RESETP pin low to apply a power-on

reset.

H-UDI reset assert H-UDI reset negate

SDIR

Chip internal reset

CPU state

Branch to H'A0000000

Figure 15.4 H-UDI Reset

15.4.5 H-UDI Interrupt

The H-UDI interrupt function generates an interrupt by setting a command from the H-UDI in the

SDIR. An H-UDI interrupt is a general exception/interrupt operation, resulting in a branch to an

address based on the VBR value plus offset, and with return by the RTE instruction. This interrupt

request has a fixed priority level of 15.

H-UDI interrupts are accepted in sleep mode.