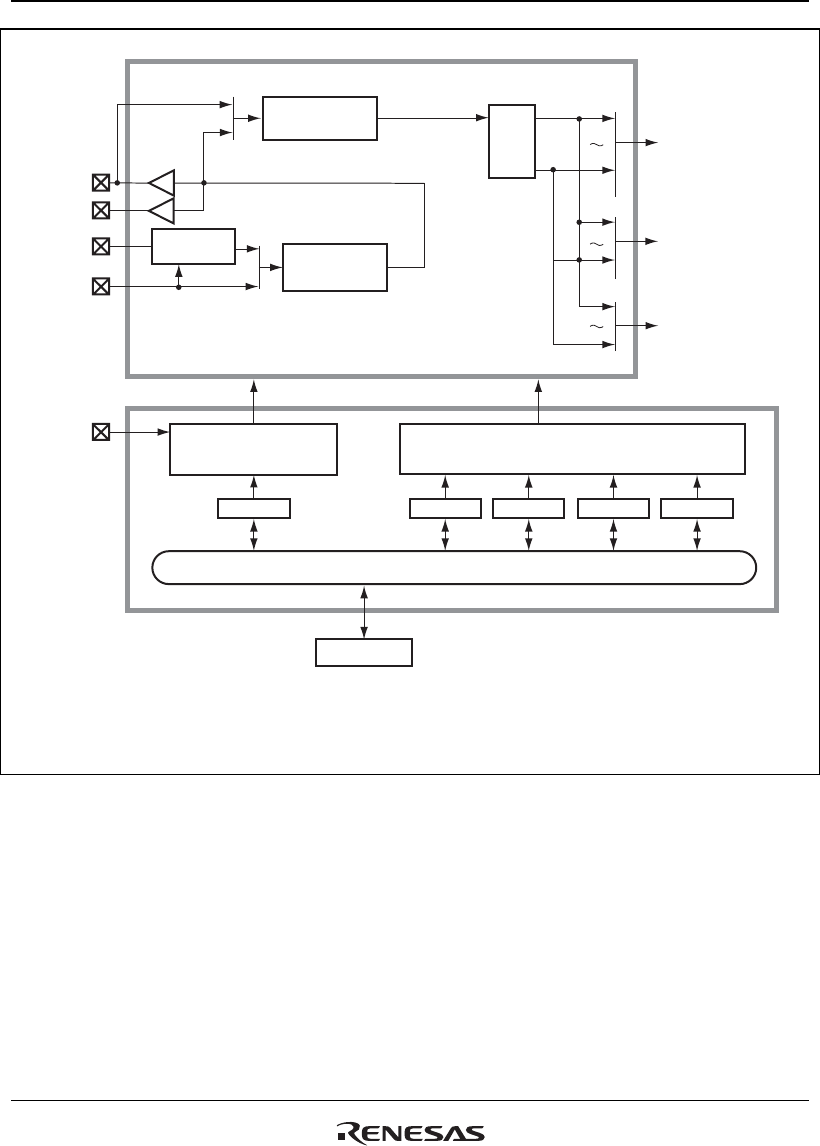

Section 4 Clock Pulse Generator (CPG)

Rev. 4.00 Sep. 14, 2005 Page 144 of 982

REJ09B0023-0400

CKIO

CKIO2

PLL circuit 1

(×1, 2, 3, 4)

×1

×1/2

×1/3

×1/4

Clock pulse generator

Divider

Internal clock

(Iφ)

Internal bus

Bus interface

FRQCR:

STBCR:

STBCR2:

STBCR3:

STBCR4:

[Legend]

Frequency control register

Standby control register

Standby control register 2

Standby control register 3

Standby control register 4

Peripheral clock

(Pφ)

Bus clock

(Bφ = CKIO)

EXTAL

MD2

MD0

XTAL

FRQCR

STBCR

STBCR2

STBCR3 STBCR4

CPG control unit

Clock frequency

control circuit

Standby control circuit

PLL circuit 2

(× 2,4)

Crystal

oscillator

Figure 4.1 Block Diagram of Clock Pulse Generator