Section 19 Serial Communication Interface with FIFO (SCIF)

Rev. 4.00 Sep. 14, 2005 Page 737 of 982

REJ09B0023-0400

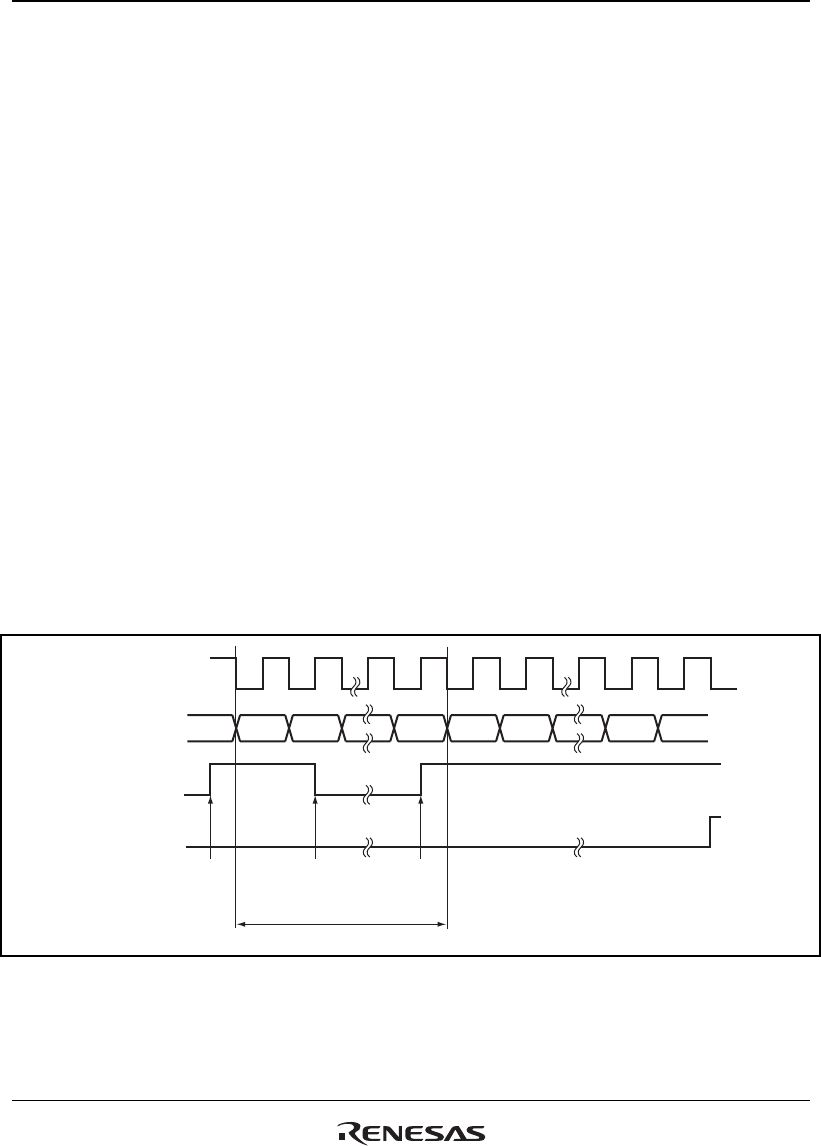

In serial transmission, the SCIF operates as described below.

1. When data is written into the transmit FIFO data register (SCFTDR), the SCIF transfers the

data from SCFTDR to the transmit shift register (SCTSR) and starts transmitting. Confirm

that the TDFE flag in the serial status register (SCFSR) is set to 1 before writing transmit data

to SCFTDR. The number of data bytes that can be written is (16 – transmit trigger setting).

2. When data is transferred from SCFTDR to SCTSR and transmission is started, consecutive

transmit operations are performed until there is no transmit data left in SCFTDR. When the

number of transmit data bytes in SCFTDR falls below the transmit trigger number set in the

FIFO control register (SCFCR), the TDFE flag is set. If the TIE bit in the serial control

register (SCSR) is set to 1 at this time, a transmit-FIFO-data-empty interrupt (TXI) request is

generated.

If clock output mode is selected, the SCIF outputs eight synchronous clock pulses. If an

external clock source is selected, the SCIF outputs data in synchronization with the input

clock. Data is output from the TxD pin in order from the LSB (bit 0) to the MSB (bit 7).

3. The SCIF checks the SCFTDR transmit data at the timing for sending the MSB (bit 7). If data

is present, the data is transferred from SCFTDR to SCTSR, the MSB (bit 7) is sent, and then

serial transmission of the next frame is started. If there is no transmit data, the TEND flag in

SCFSR is set to 1, the MSB (bit 7) is sent, and then the TxD pin holds the states.

4. After the end of serial transmission, the SCK pin is held in the high state.

Figure 19.14 shows an example of SCIF transmit operation.

Synchronization

clock

Serial data

TDFE

TEND

Data written to SCFTDR

and TDFE flag cleared

to 0 by TXI interrupt

handler

One frame

Bit 0

LSB

TXI

interrupt

request

MSB

Bit 1 Bit 6 Bit 7Bit 7 Bit 0 Bit 1

TXI

interrupt

request

Figure 19.14 Example of SCIF Transmit Operation