Section 17 Compare Match Timer (CMT)

Rev. 4.00 Sep. 14, 2005 Page 514 of 982

REJ09B0023-0400

17.4 Compare Matches

17.4.1 Timing of Compare Match Flag Setting

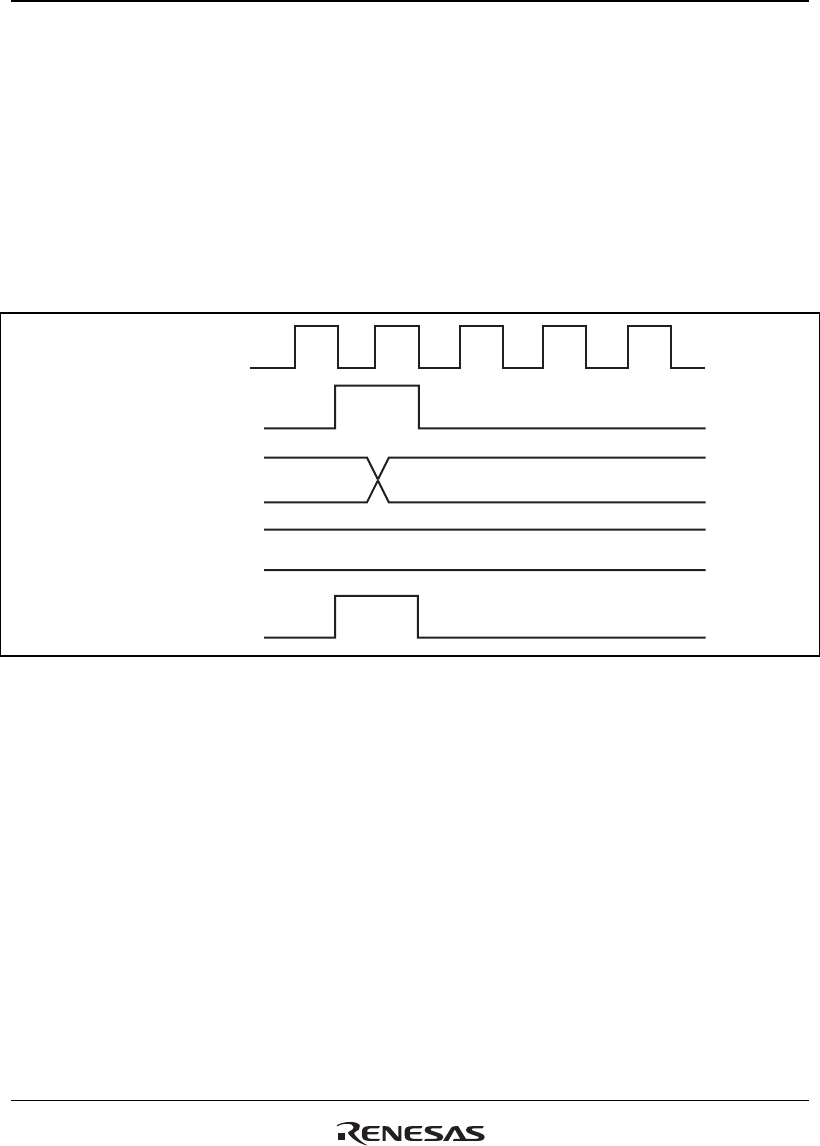

When CMCOR and CMCNT match, a compare match signal is generated and the CMF bit in

CMCSR is set to 1. The compare match signal is generated in the last state in which the values

match (when the CMCNT value is updated to H'0000). That is, after a match between CMCOR

and CMCNT, the compare match signal is not generated until the next CMCNT counter clock

input. Figure 17.4 shows the timing of CMF bit setting.

N

Peripheral operating

clock (Pφ)

Counter clock

CMCNT

CMCOR

Compare match

signal

Clock

N + 1

N

0

Figure 17.4 Timing of CMF Setting

17.4.2 DMA Transfer Requests and Interrupt Requests

Generation of a DMA transfer request or an interrupt request when a compare match occurs can be

selected with bits CMR1 and CMR0 in CMCSR.

With a DMA transfer request, the request signal is cleared automatically when the DMAC accepts

the request. However, the CMF bit in CMCSR is not cleared to 0.

An interrupt request is cleared by writing 0 to the CMF bit in CMCSR. Therefore, an operation to

set CMF = 0 must be performed by the user in the exception handling routine. If this operation is

not carried out, another interrupt will be generated.