Section 19 Serial Communication Interface with FIFO (SCIF)

Rev. 4.00 Sep. 14, 2005 Page 740 of 982

REJ09B0023-0400

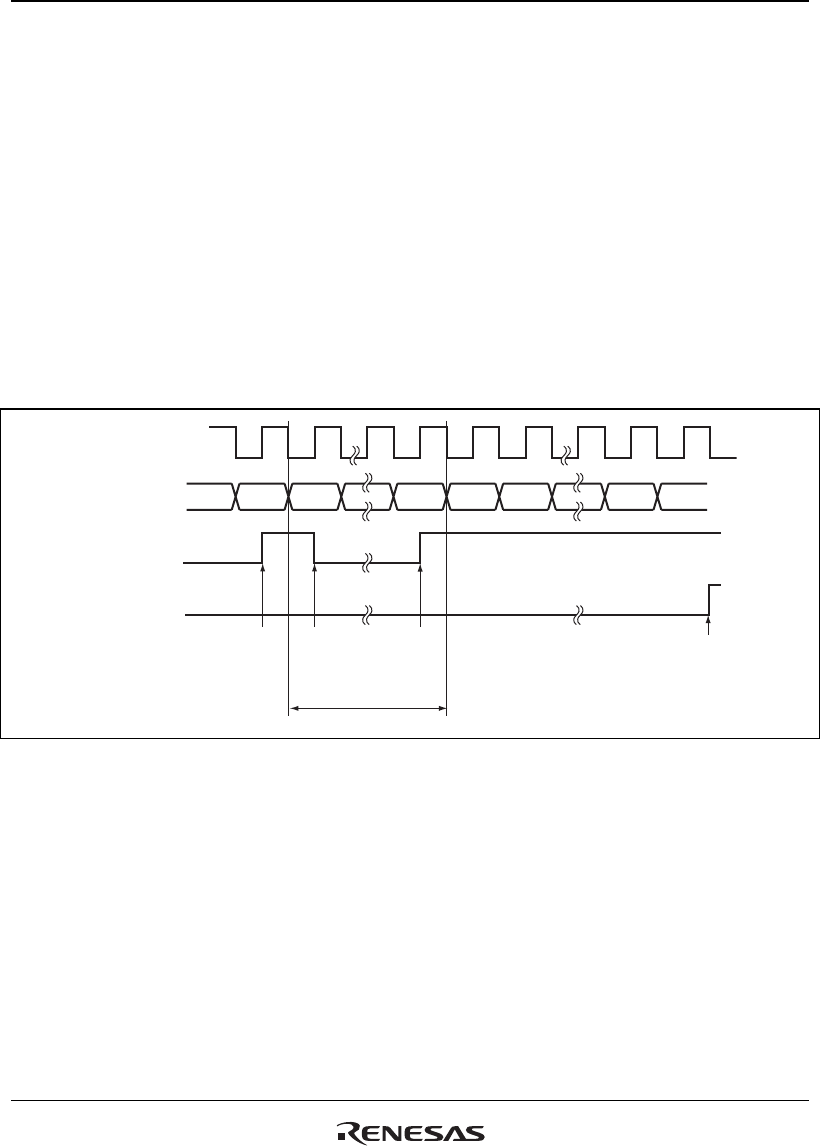

In serial reception, the SCIF operates as described below.

1. The SCIF synchronizes with serial clock input or output and starts the reception.

2. Receive data is shifted into SCRSR in order from the LSB to the MSB. After receiving the

data, the SCIF checks the receive data can be loaded from SCRSR into SCFRDR or not. If this

check is passed, the SCIF stores the received data in SCFRDR. If the check is not passed

(overrun error is detected), further reception is prevented.

3. After setting RDF to 1, if the receive-data-full interrupt enable bit (RIE) is set to 1 in SCSCR,

the SCIF requests a receive-data-full interrupt (RXI). If the ORER bit is set to 1 and the

receive-data-full interrupt enable bit (RIE) or the receive error interrupt enable bit (REIE) in

SCSCR is also set to 1, the SCIF requests a break interrupt (BRI).

Figure 19.17 shows an example of SCIF receive operation.

Synchronization

clock

Serial data

RDF

ORER

Data read from

SCFRDR and

RDF flag cleared

to 0 by RXI

interrupt handler

One frame

Bit 7

LSB

RXI

interrupt

request

MSB

Bit 0 Bit 6 Bit 7Bit 7 Bit 0 Bit 1

BRI interrupt request

by overrun error

RXI

interrupt

request

Figure 19.17 Example of SCIF Receive Operation