Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 350 of 982

REJ09B0023-0400

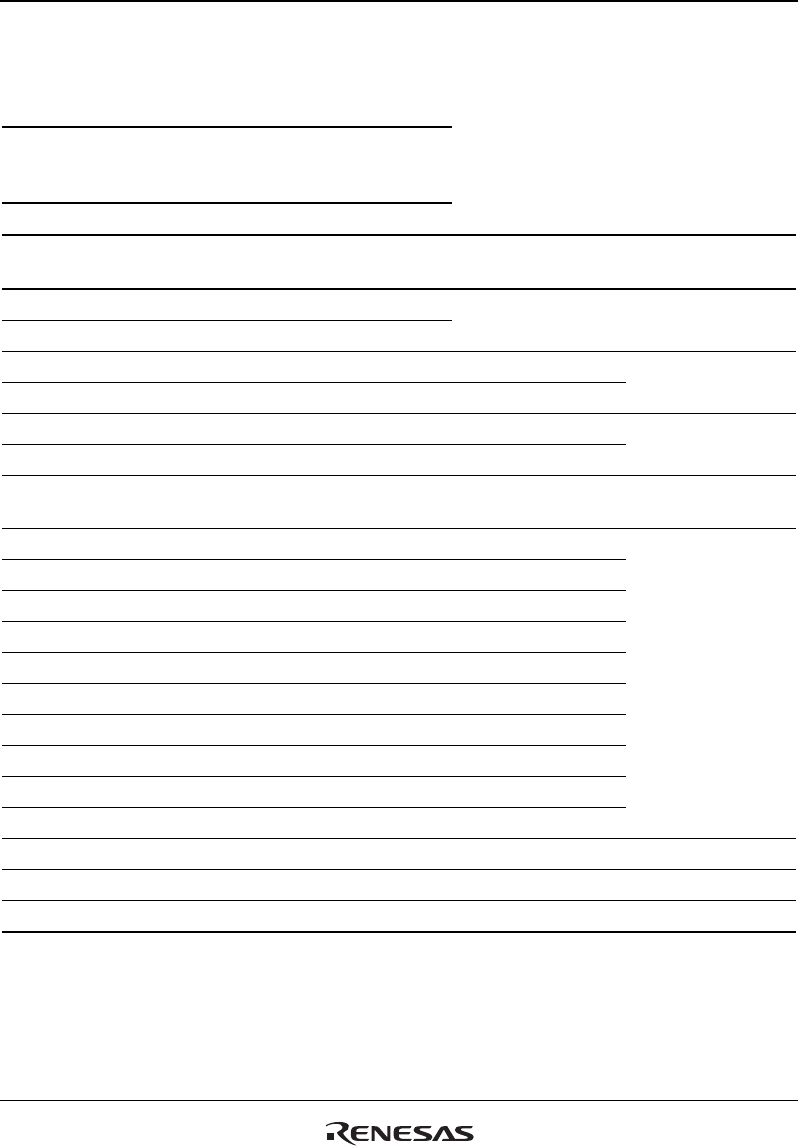

Table 12.13 Relationship between BSZ1, 0, A2/3ROW1, 0, and Address Multiplex Output

(6)-2

Setting

BSZ

1, 0

A2/3

ROW

1, 0

A2/3

COL

1, 0

11 (32 bits) 00 (11 bits) 00 (8 bits)

Output Pin of

This LSI

Row Address

Output Cycle

Column Address

Output Cycle

SDRAM Pin Function

A17 A27 A17

A16 A26 A16

Unused

A15 A25*

2

A25*

2

*

3

A14 (BA1)

A14 A24*

2

A24*

2

A13 (BA0)

Specifies bank

A13 A23 A13 A12

A12 A22 A12 A11

Address

A11 A21 L/H*

1

A10/AP Specifies

address/precharge

A10 A20*

2

A10 A9

A9 A19 A9 A8

A8 A18 A8 A7

A7 A17 A7 A6

A6 A16 A6 A5

A5 A15 A5 A4

A4 A14 A4 A3

A3 A13 A3 A2

A2 A12 A2 A1

A1 A11 A1 A0

Address

A0 A10 A0 Unused

Example of connected memory

512-Mbit product (8 Mwords × 16 bits × 4 banks, column 10 bits product): 1

Notes: 1. L/H is a bit used in the command specification; it is fixed at L or H according to the

access mode.

2. Bank address specification

3. Only the RASL pin is asserted because the A25 pin specified the bank address. RASU

is not asserted.