Section 3 DSP Operation

Rev. 4.00 Sep. 14, 2005 Page 140 of 982

REJ09B0023-0400

31

15 1

0

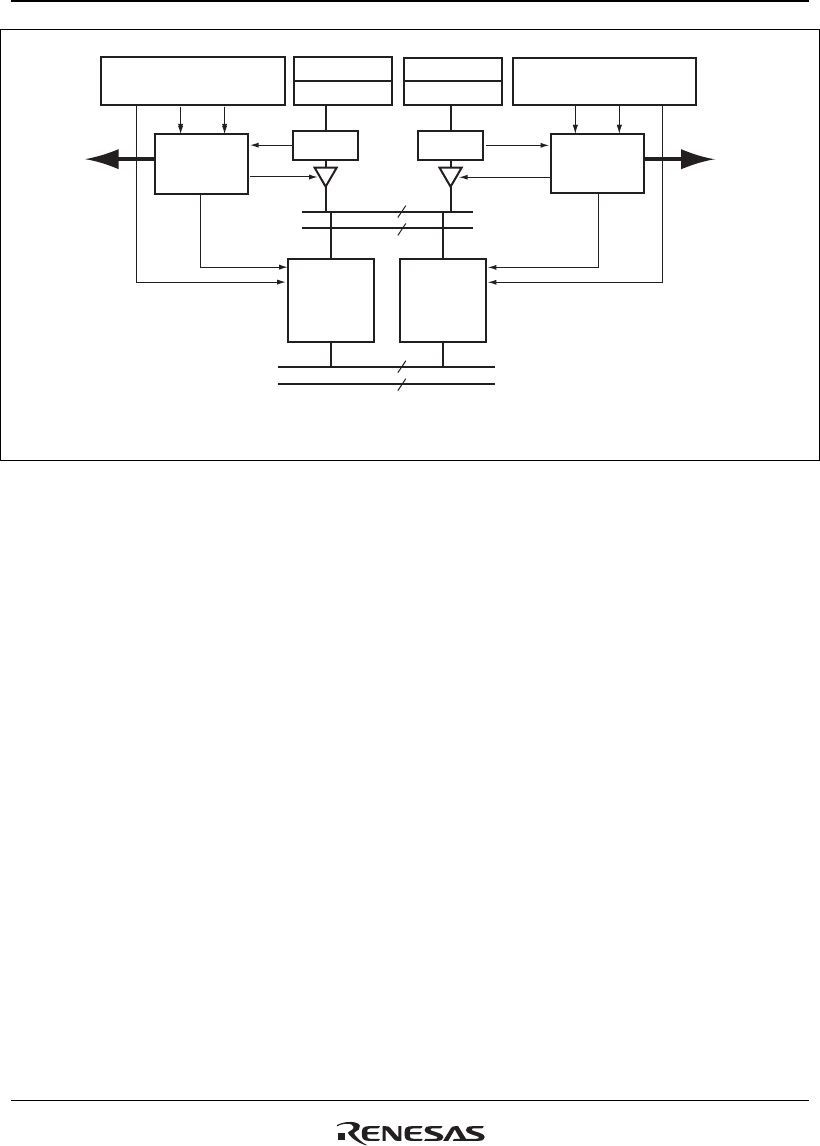

R4 [Ax]

R5 [Ax]

ABx

XAB 16-bit

X_MEM

X R/W

Y_MEM

Y R/W

YAB 16-bit

XDB

YDB

16-bit

16-bit

X data

memory

4 kbytes

31

15 1

0

R6 [Ay]

R7 [Ay]

ABy

Y data

memory

4 kbytes

X_MEM and Y_MEM:

Select X and Y data memory

Instruction code for X

data-transfer operation

Instruction code for Y

data-transfer operation

Control

for X memory

Control

for Y memory

Input/output

control for

DSP data

registers

X0/X1, A0/A1

Input/output

control for

DSP data

registers

Y0/Y1, A0/A1

Figure 3.22 Load/Store Control for X and Y Data-Transfer Instructions

Control for X Memory:

if ( !Nop ) {

X_MEM=1; XAB=ABx;

if ( load operation ) {

Dx[31:16]=XDB;

Dx[15:0]=0x0000; /* Dx is X0 or X1 */

}

else XDB = Dx[31:16]; /* Dx is A0 or A1 */

}

else { X_MEM=0; XAB=0x000; }

The conditional execution based on the DC flag in DSR cannot control any MOVX/MOVY

instructions.