Section 13 Direct Memory Access Controller (DMAC)

Rev. 4.00 Sep. 14, 2005 Page 449 of 982

REJ09B0023-0400

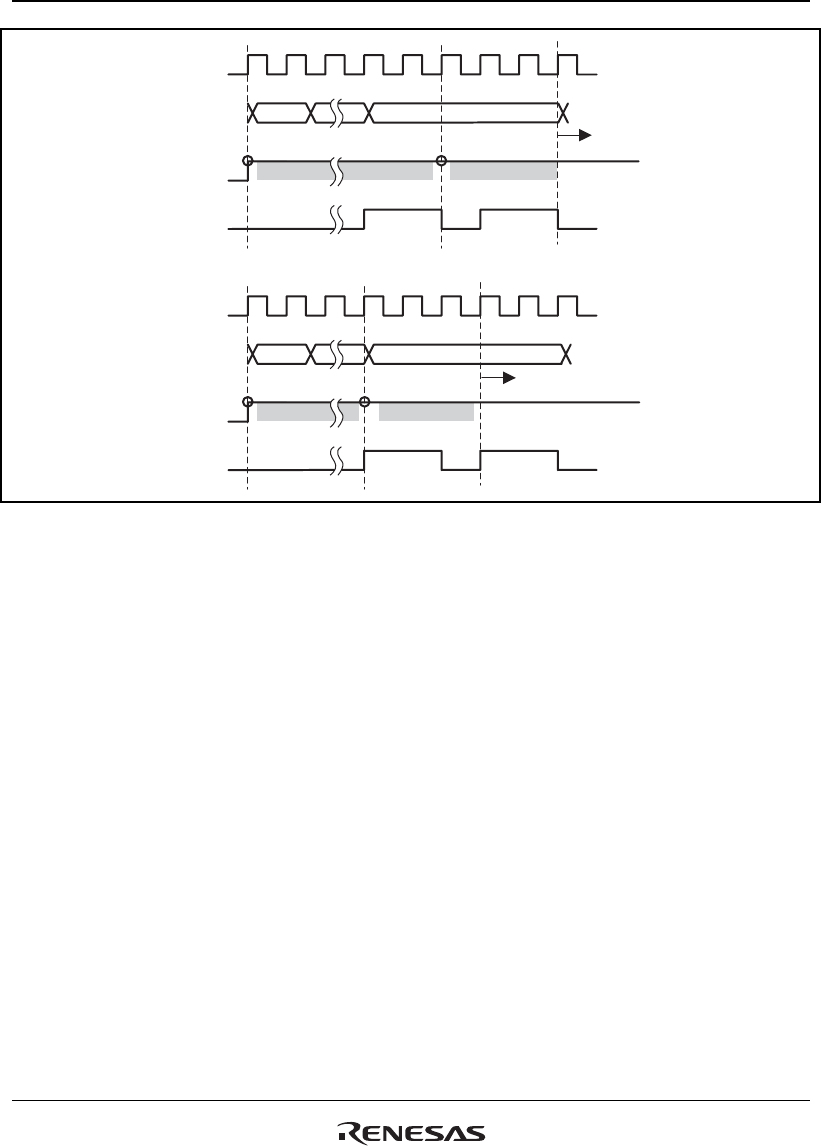

CPU

CPU

DMAC write

DMAC write

Non-sensitive period

1st acceptance 2nd acceptance

3rd acceptance possible

3rd acceptance possible

Non-sensitive period

Non-sensitive period

1st acceptance 2nd acceptance

Non-sensitive period

DREQ

(Overrun 1,

high-level)

DACK

(High-active)

CKIO

Bus cycle

DREQ

(Overrun 0,

high-level)

DACK

(High-active)

CKIO

Bus cycle

Figure 13.22 Example of DREQ Input Detection in Cycle Steal Mode Level Detection

When DACK is Divided to 2 by Idle Cycles

(3) Notes

For the external access described in (2) above, note the following.

1. When the DREQ edge is detected, input one DREQ edge at maximum in the bus cycle.

2. When the DREQ level is detected in overrun 0, negate the DREQ input in the bus cycle after

the detection of the first DACK output negation and before the second DACK output negation.

3. When the DREQ level is detected in overrun 1, negate DREQ input after the detection of the

first DACK output assertion and before the second DACK output assertion.