Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 37 of 982

REJ09B0023-0400

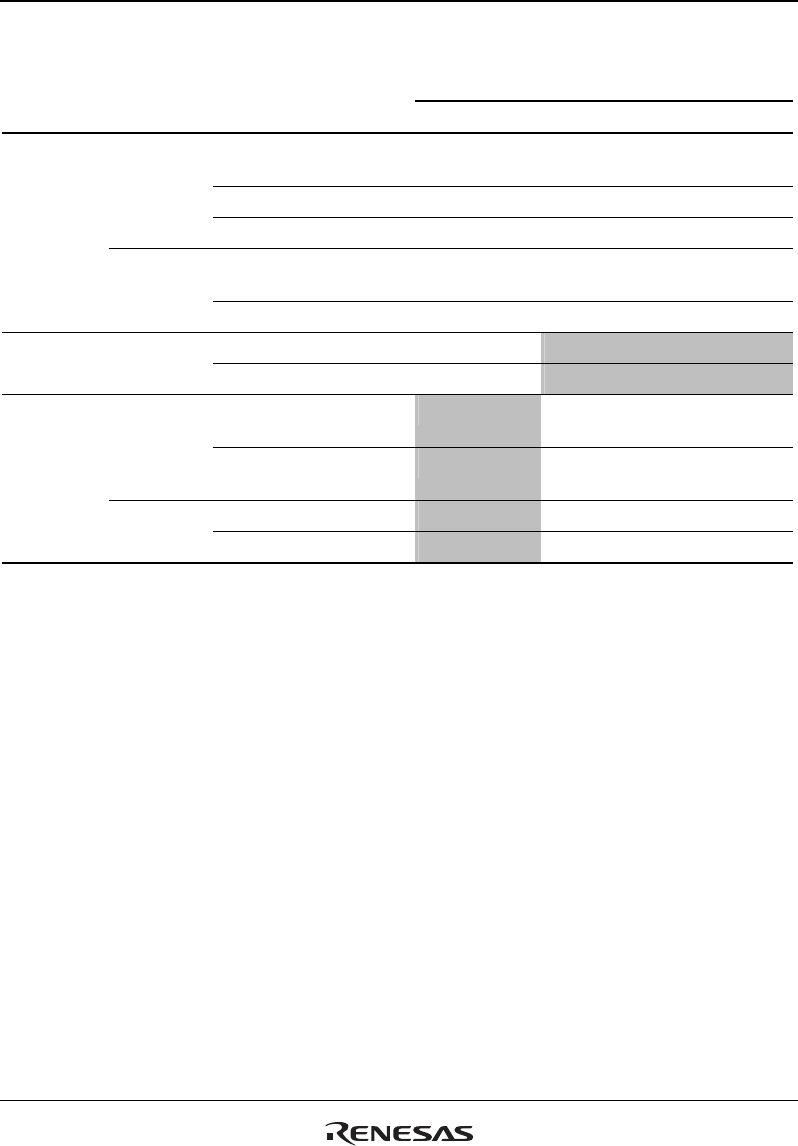

Table 2.2 Destination Register in DSP Instructions

Guard Bits Register Bits

Registers Instructions 39 32 31 16 15 0

A0, A1 DSP Fixed-point, PSHA,

PMULS

Sign-extended 40-bit result

Integer, PDMSB Sign-extended 24-bit result Cleared

Logical, PSHL Cleared 16-bit result Cleared

Data

transfer

MOVS.W Sign-extended 16-bit data Cleared

MOVS.L Sign-extended 32-bit data

A0G, A1G MOVS.W Data No update

Data

transfer

MOVS.L Data

No update

DSP Fixed-point, PSHA,

PMULS

32-bit result X0, X1

Y0, Y1

M0, M1

Integer, logical,

PDMSB, PSHL

16-bit result Cleared

MOVX/Y.W, MOVS.W 16-bit result Cleared

Data

transfer

MOVS.L 32-bit data