Section 25 Electrical Characteristics

Rev. 4.00 Sep. 14, 2005 Page 938 of 982

REJ09B0023-0400

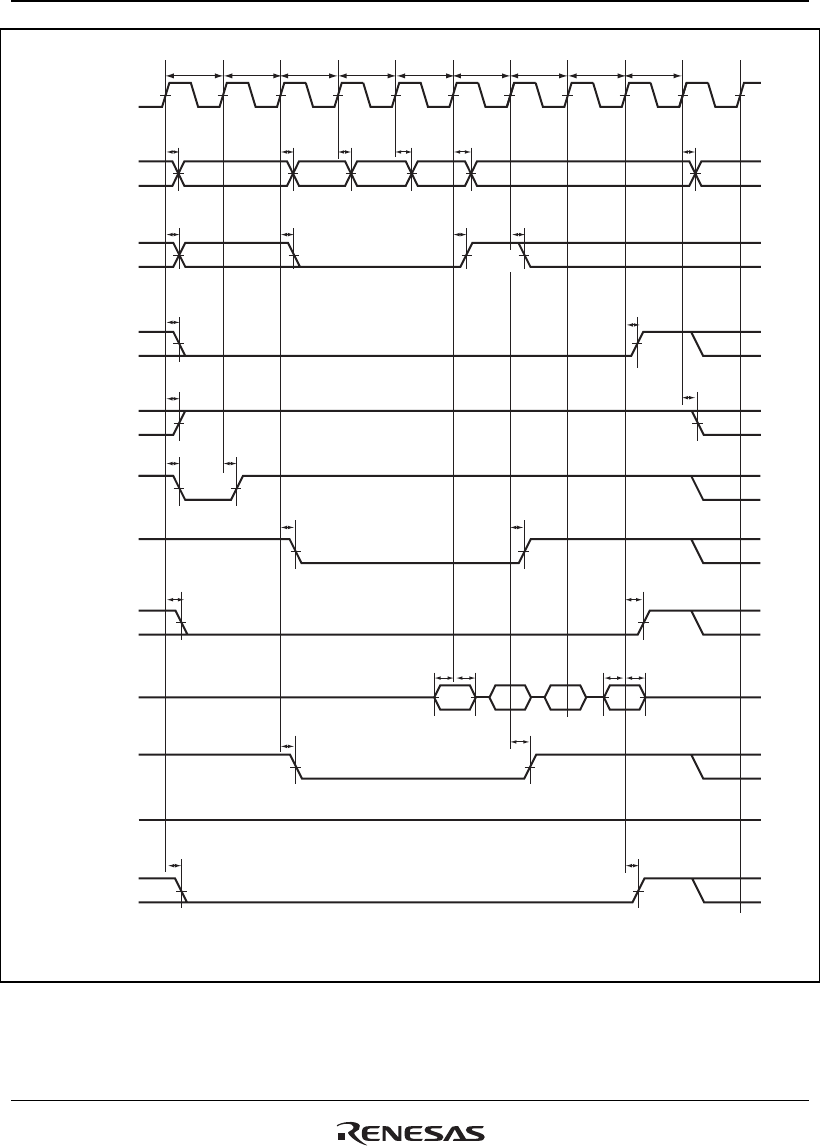

Tc1 Tc2

Td1 Td2 Td3 Td4

Tr Trw Tc3 Tc4 Tde

t

AD1

t

AD1

t

CSD1

t

AD1

t

AD1

t

AD1

t

AD1

t

RWD1

t

RWD1

t

CSD1

t

AD1

t

AD1

t

AD1

t

AD1

t

RDH2

t

RDS2

CKIO

A25 to A0

CSn

RD/WR

A12/A11*

1

D31 to D0

t

RASD1

t

RASD1

RASU/L

Row

address

Read command

Column

address

(1 to 4)

t

CASD1

t

CASD1

CASU/L

t

BSD

t

BSD

(High)

BS

CKE

t

DQMD1

t

DQMD1

DQMxx

t

DACD

t

DACD

DACKn*

2

t

RDH2

t

RDS2

ReadA

command

Note: 1. An address pin to be connected to pin A10 of SDRAM.

2. Waveform for DACKn when active low is selected.

Figure 25.26 Synchronous DRAM Burst Read Bus Cycle (Four Read Cycles)

(Auto Precharge, CAS Latency 2, WTRCD = 1 Cycle, WTRP = 0 Cycle)