Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 65 of 982

REJ09B0023-0400

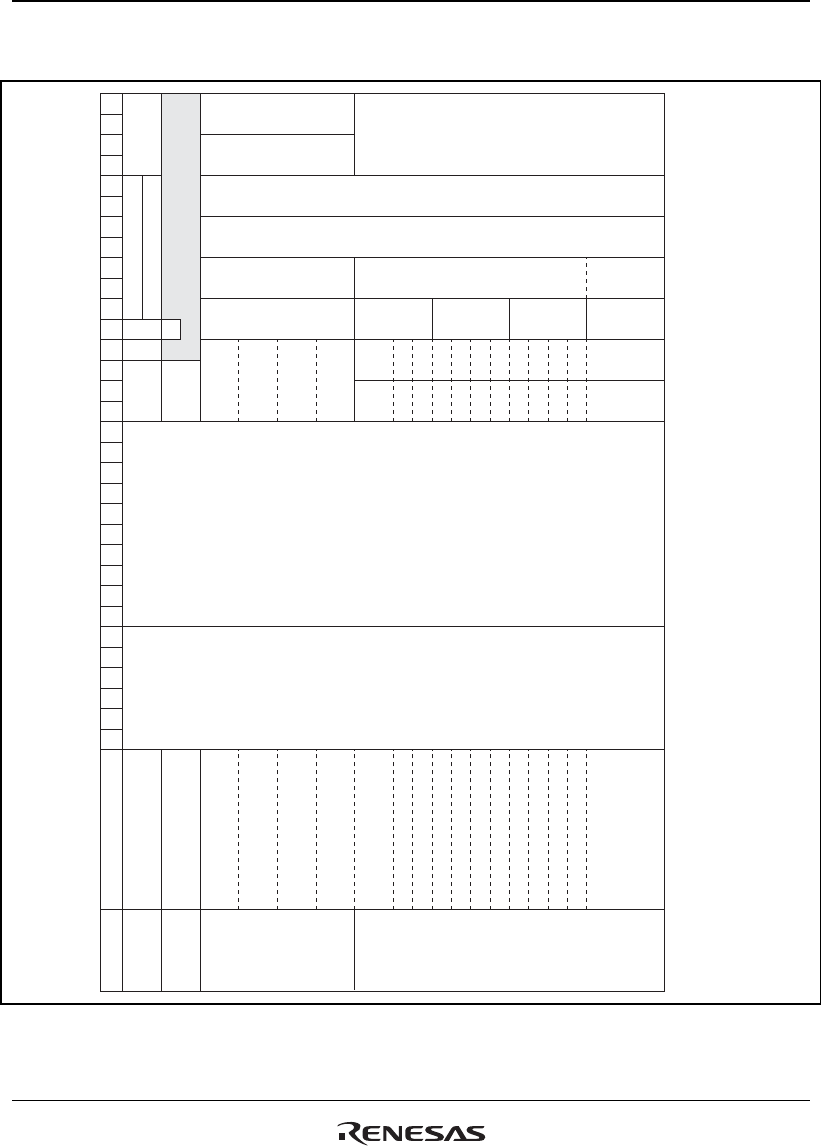

Table 2.17 B-Field ALU Operation Instructions and Multiply Instructions (1)

PSHL #imm, Dz

PSHA #imm, Dz

Reserved

PMULS Se, Sf, Dg

Reserved

PSUB Sx, Sy, Du

PMULS Se, Sf, Dg

PADD Sx, Sy, Du

PMULS Se, Sf, Dg

Reserved

PSUBC Sx, Sy, Dz

PADDC Sx, Sy, Dz

PCMP Sx, Sy

Reserved

Reserved

Reserved

PABS Sx, Dz

PRND Sx, Dz

PABS Sy, Dz

PRND Sy, Dz

Reserved

Mnemonic

imm. shift

Type

0:(*

1

)

1:(*

1

)

2:(*

1

)

3:(*

1

)

4:(*

1

)

5:A1

6:(*

1

)

7:A0

8:X0

9:X1

A:Y0

B:Y1

C:M0

D:(*

1

)

E:M1

F:(*

1

)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

6-operand

parallel

instructions

3-operand

instructions

111110 0

0

0

0

0

0

0

0

1

0

0

0

0

1

1

1

1

0

0

0

0

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

1

–16 < = imm < = +16

–32 < = imm < = +32

Se Sf Sx Sy Dg

Du

0:X0

1:X1

2:Y0

3:A1

0:Y0

1:Y1

2:X0

3:A1

0:X0

1:X1

2:A0

3:A1

0:Y0

1:Y1

2:M0

3:M1

0:M0

1:M1

2:A0

3:A1

0:X0

1:Y0

2:A0

3:A1

0

0

1

1

0

1

0

1

0

0

Dz

Dz

Note: 1. Codes reserved for system use.

A field