Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 72 of 982

REJ09B0023-0400

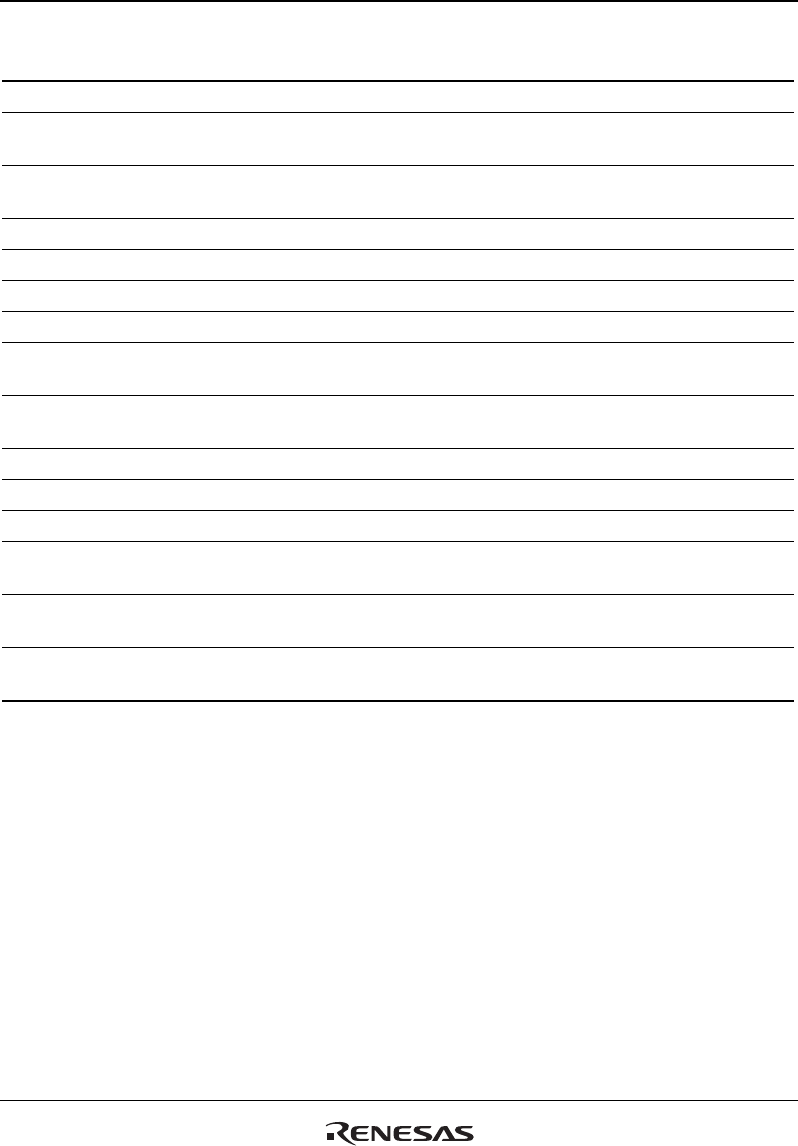

Instruction

Instruction Code

Operation

Execution

States

T Bit

MOV.L Rm,@(R0,Rn) 0000nnnnmmmm0110 Rm → (R0 + Rn) 1 —

MOV.B @(R0,Rm),Rn 0000nnnnmmmm1100 (R0 + Rm) → Sign extension

→ Rn

1 —

MOV.W @(R0,Rm),Rn 0000nnnnmmmm1101 (R0 + Rm) → Sign extension

→ Rn

1 —

MOV.L @(R0,Rm),Rn 0000nnnnmmmm1110 (R0 + Rm) → Rn 1 —

MOV.B R0,@(disp,GBR) 11000000dddddddd R0 → (disp + GBR) 1 —

MOV.W R0,@(disp,GBR) 11000001dddddddd R0 → (disp × 2 + GBR) 1 —

MOV.L R0,@(disp,GBR) 11000010dddddddd R0 → (disp × 4 + GBR) 1 —

MOV.B @(disp,GBR),R0 11000100dddddddd (disp + GBR) → Sign

extension → R0

1 —

MOV.W @(disp,GBR),R0 11000101dddddddd (disp × 2 + GBR) →

Sign extension → R0

1 —

MOV.L @(disp,GBR),R0 11000110dddddddd (disp × 4 + GBR) → R0 1 —

MOVA @(disp,PC),R0 11000111dddddddd disp × 4 + PC → R0 1 —

MOVT Rn 0000nnnn00101001 T → Rn 1 —

SWAP.B Rm,Rn 0110nnnnmmmm1000 Rm → Swap lowest two

bytes → Rn

1 —

SWAP.W Rm,Rn 0110nnnnmmmm1001 Rm → Swap two consecutive

words → Rn

1 —

XTRCT Rm,Rn 0010nnnnmmmm1101 Middle 32 bits of Rm and

Rn → Rn

1