Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 351 of 982

REJ09B0023-0400

Burst Read: A burst read occurs in the following cases with this LSI.

• Access size in reading is larger than data bus width.

• 16-byte transfer in cache error.

• 16-byte transfer in DMAC

This LSI always accesses the SDRAM with burst length 1. For example, read access of burst

length 1 is performed consecutively 4 times to read 16-byte continuous data from the SDRAM that

is connected to a 32-bit data bus.

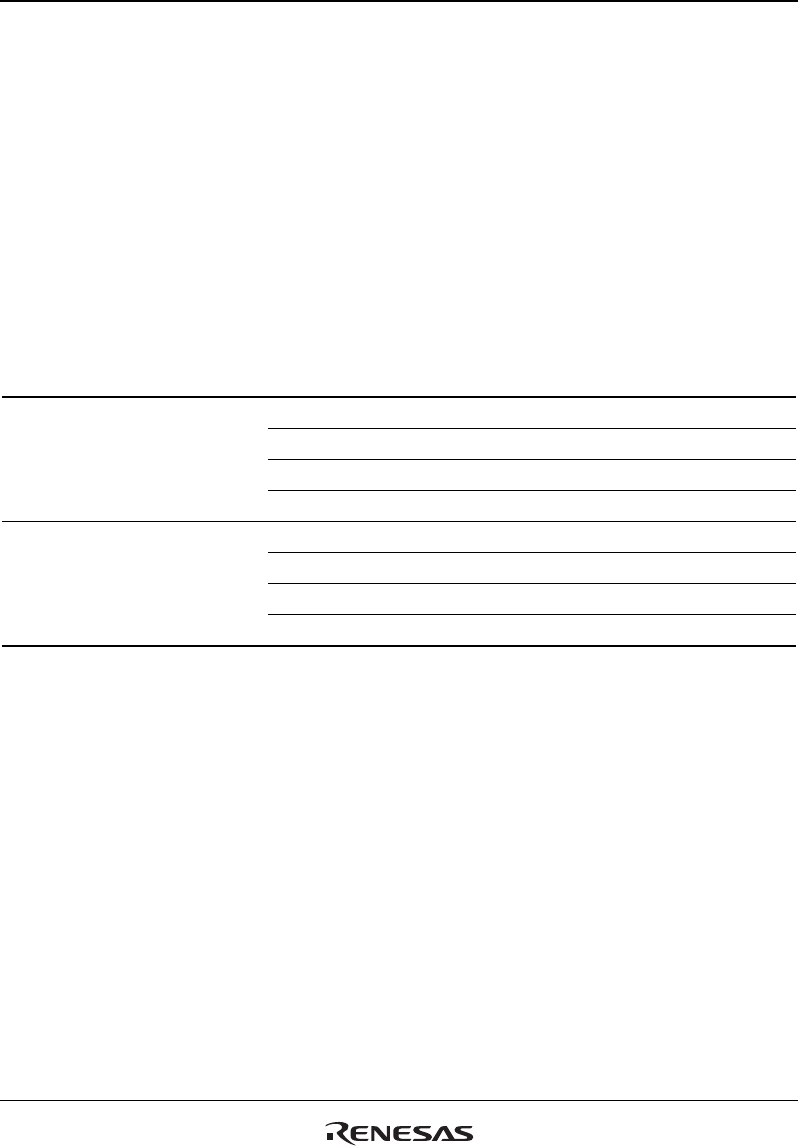

Table 12.14 shows the relationship between the access size and the number of bursts.

Table 12.14 Relationship between Access Size and Number of Bursts

Bus Width Access Size Number of Bursts

16 bits 8 bits 1

16 bits 1

32 bits 2

16 bits 8

32 bits 8 bits 1

16 bits 1

32 bits 1

16 bits 4

Figures 12.18 and 12.19 show a timing chart in burst read. In burst read, an ACTV command is

output in the Tr cycle, the READ command is issued in the Tc1, Tc2, and Tc3 cycles, the READA

command is issued in the Tc4 cycle, and the read data is received at the rising edge of the external

clock (CKIO) in the Td1 to Td4 cycles. The Tap cycle is used to wait for the completion of an

auto-precharge induced by the READA command in the SDRAM. In the Tap cycle, a new

command will not be issued to the same bank. However, access to another CS space or another

bank in the same SDRAM space is enabled. The number of Tap cycles is specified by the WTRP1

and WTRP0 bits in the CS3WCR register.

In this LSI, wait cycles can be inserted by specifying each bit in the CS3WCR register to connect

the SDRAM in variable frequencies. Figure 12.19 shows an example in which wait cycles are

inserted. The number of cycles from the Tr cycle where the ACTV command is output to the Tc1

cycle where the READ command is output can be specified using the WTRCD1 and WTRCD0

bits in the CS3WCR register. If the WTRCD1 and WTRCD0 bits specify one cycles or more, a

Trw cycle where the NOT command is issued is inserted between the Tr cycle and Tc1 cycle. The