Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 48 of 982

REJ09B0023-0400

2.4 Instruction Formats

2.4.1 CPU Instruction Addressing Modes

The following table shows addressing modes and effective address calculation methods for

instructions executed by the CPU core.

Table 2.11 Addressing Modes and Effective Addresses for CPU Instructions

Addressing

Mode

Instruction

Format

Effective Address Calculation Method Calculation Formula

Register direct Rn Effective address is register Rn.

(Operand is register Rn contents.)

Register indirect @Rn Effective address is register Rn contents.

Rn

Rn

Rn

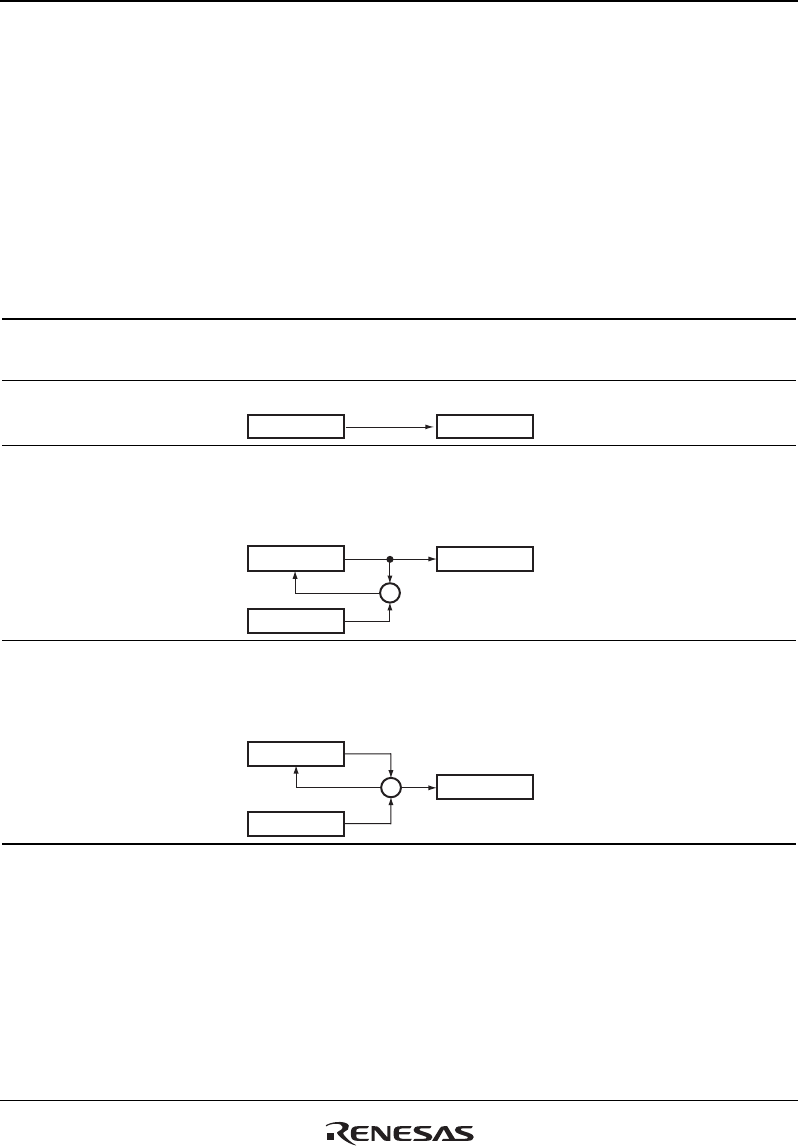

Register

indirect with

post-increment

@Rn+ Effective address is register Rn contents.

A constant is added to Rn after instruction

execution: 1 for a byte operand, 2 for a word

operand, 4 for a longword operand.

Rn

Rn

1/2/4

+

Rn + 1/2/4

Rn

After instruction execution

Byte: Rn + 1 → Rn

Word: Rn + 2 → Rn

Longword: Rn + 4 → Rn

Register

indirect with

pre-decrement

@–Rn Effective address is register Rn contents. It is

decremented by a constant beforehand: 1 for

a byte operand, 2 for a word operand, 4 for

a longword operand.

Rn

1/2/4

Rn – 1/2/4

–

Rn – 1/2/4

Byte: Rn – 1 → Rn

Word: Rn – 2 → Rn

Longword: Rn – 4 → Rn

(Instruction executed with Rn

after calculation)