107

Chapter 4 CPU Architecture

3.CPU

3. CPU

The CPU realizes the compact implementation of a 32-bit RISC FR architecture.

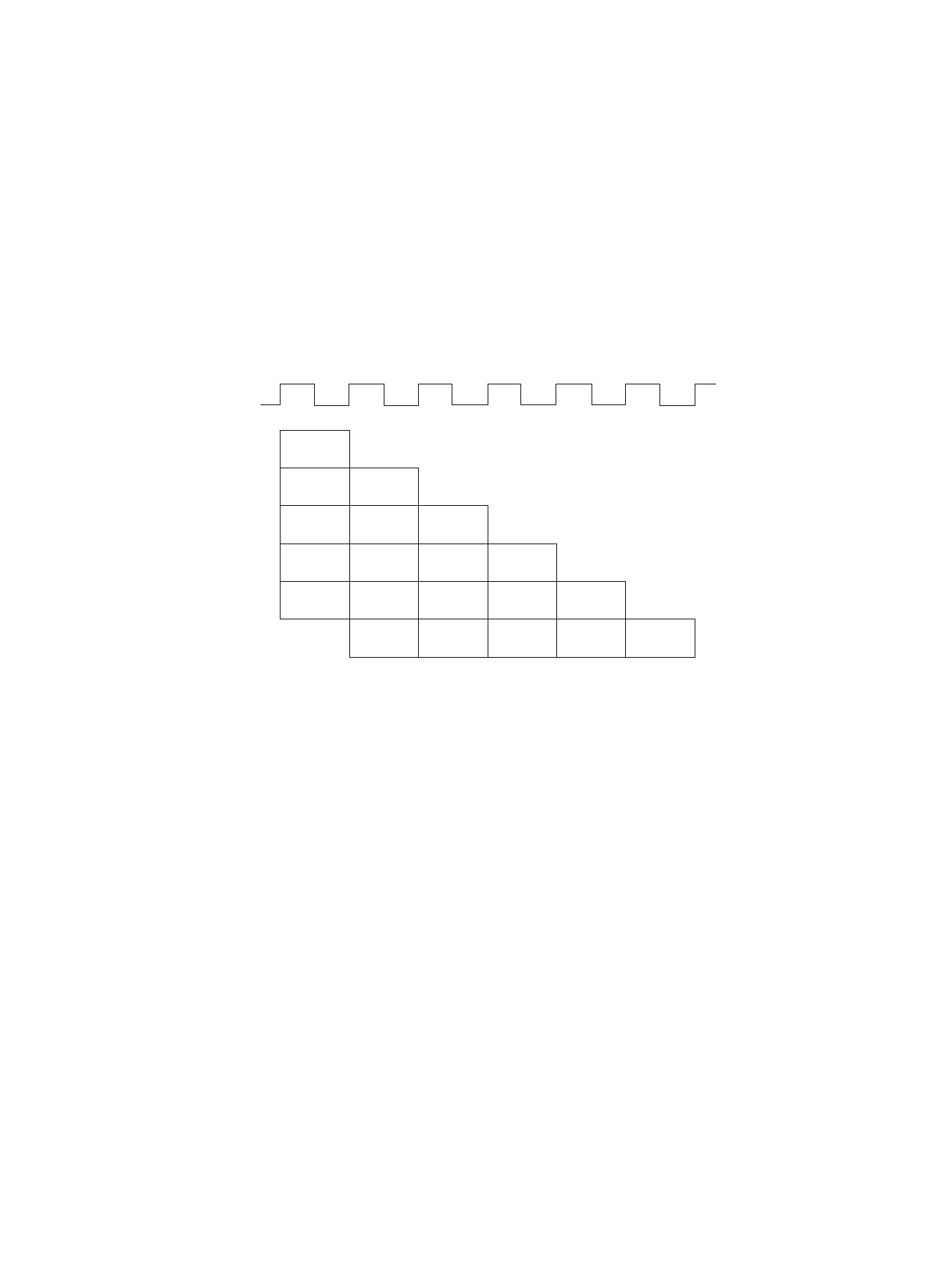

It employs a 5-stage instruction pipeline method to execute 1 instruction per 1 cycle.

This pipeline consists of the following stages.

• Instruction fetch (IF): outputs instruction address to fetch instruction.

• Instruction decode (ID): decodes fetched instruction and reads register.

• Execution (EX): executes operation.

• Memory access (MA): loads data for memory or accesses stored data.

• Write back to register (WB): writes back data to registers.

Figure 3-1 Instruction Pipeline

No instruction is executed in random order. If instruction A enters into pipeline before instruction B, instruction

A always reaches to write-back stage before instruction B.

1 instruction is executed per 1 cycle.

However, to execute the instruction, multiple cycles are required for load/store instruction with memory wait,

branch instruction without delay slot and multi-cycle instruction. In addition, a slow instruction degrades

instruction execution speed.

4. 32-bit/16-bit Bus Converter

This converter generates the interface between D-bus which executes 32-bit high-speed access and R-bus

which executes 16-bit access in order to realize data access from CPU to peripheral functions.

If 32-bit access comes from CPU, this converter converts the access into two 16-bit accesses to access to R

bus. Some peripheral functions have restrictions of access width.

5. Harvard/Princeton Bus Converter

This converter realizes interface between instruction access and data access of CPU, to realize smooth

interface with external bus.

The CPU employs the Harvard architecture whose instruction bus and data bus are independent while it

employs single-bus Princeton architecture for bus controller to control external bus. This bus converter

prioritizes instruction accesses and data accesses of CPU, and executes access control to bus controller. This

always optimizes access sequence to external bus.

CLK

WB

WB

MA

EX

EX

EX

EX

ID

ID

ID

IF

IF

MA

MA

MA

MA

WB

WB

WB

WB

Instruction 1

Instruction 2

Instruction 3

Instruction 4

Instruction 5

Instruction 6