797

Chapter 39 Programmable Pulse Generator

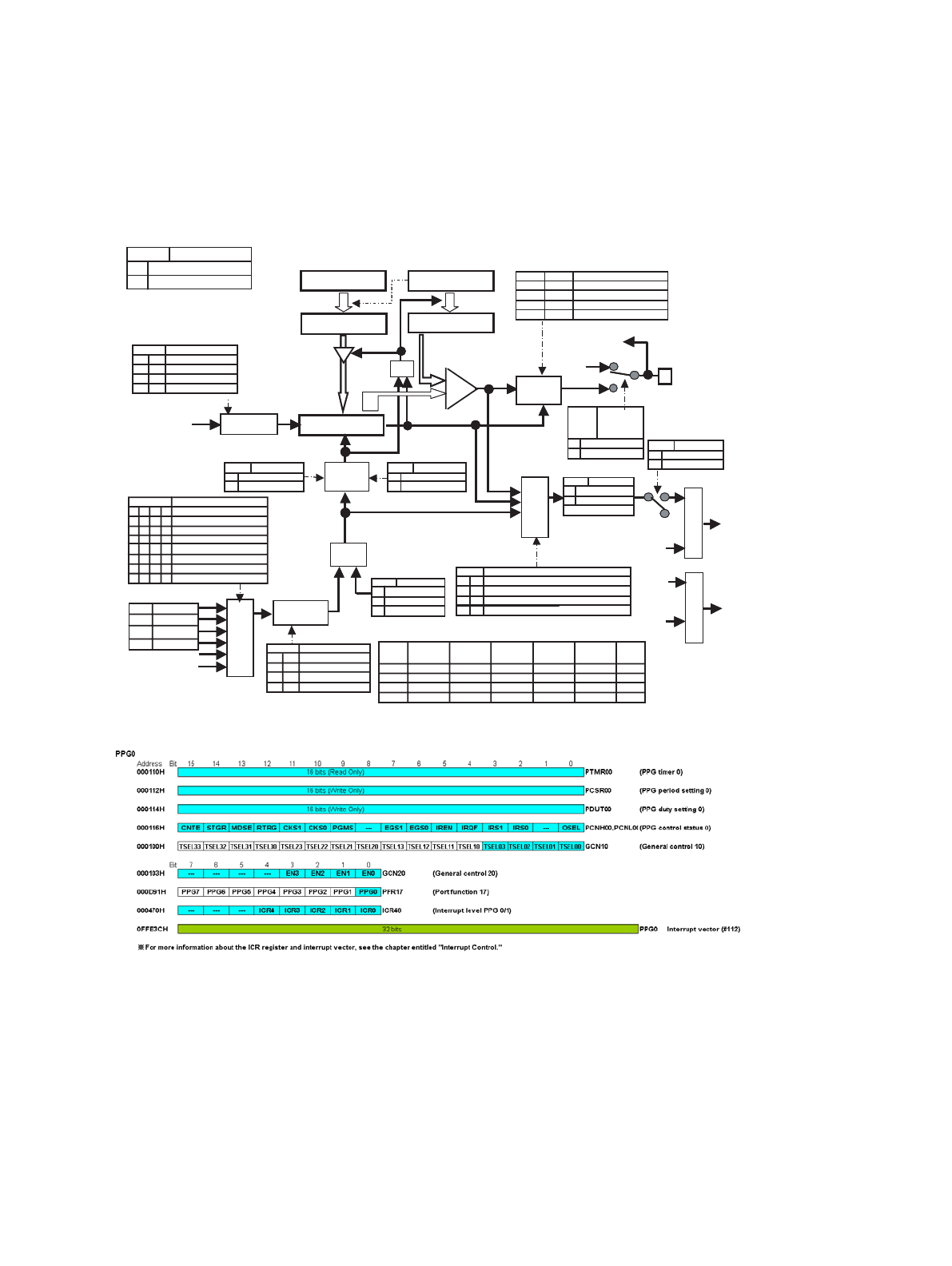

3.Configuration

3. Configuration

Figure 3-1 Configuration Diagram

Figure 3-2 Register List

OR

Trigger

OR

MDSE PCNH: bit13

0

1

PWM operation

One shot

PPG (0-3)

PCSR PDUT

Reload

Duty value

Only write

enabled

Period value

Only write

enabled

Buffers

Buffers

Compare

CKS1,0 PCNH: bit11,10

1

CLKP/64

1

0

CLKP/16

1

1

CLKP/4

0

0

CLKP

0

Prescaler

Peripheral

clock

(CLKP)

Borrow

Duty match

Read-only

down counter

OR

Enable operation/Stop

Count clock

PTMR

Duty

match

CNTE PCNH: bit15

0

1

Stop

Enable operation

RTRG PCNH: bit12

0

1

Restart disabled

Restart enabled

Control

circuit

OSEL PCNH: bit9,PCNL:bit0

Clamped H output1

Clamped L output1

Inverted output

0

Normal output

0

PGMS

1

0

1

0

Trigger selection

TSEL03-00

1000

0000

0010

0100

1010

1100

- Disabled--1

-

Disabled

110

16-bit reload timer ch0

16-bit reload timer ch1

GCN20 EN3 bit

GCN10: bit3-0

GCN20 EN2 bit

GCN20 EN1 bit

GCN20 EN0 bit

OR

Edge

selection

STGR PCNH: bit14

0

1

Operation unaffected

Software trigger

Read: Always '0'

Selector

IRS1,0 PCNL: bit3,2

1

Counter borrow or duty match

1

0

Duty match

1

1

Counter borrow

0

0

Software trigger, or trigger input available

0

Selector

Interrupt cause selection

Trigger

Borrow

Reload timer ch0

Reload timer ch1

EN0 GCN20: bit0

EN1 GCN20: bit1

EN2 GCN20: bit2

EN3 GCN20: bit3

EGS1,0 PCNL: bit7,6

Both edges

Falling edge

Rising edge

Operation unaffected

Edge selection

11

01

10

00

Timer

Period

setting

Duty

setting

Control

status H

Controls

status L

PPG

Pin

PTMR0 PCSR0 PDUT0 PCNH0 PCNL0

PTMR1 PCSR1 PDUT1 PCNH1 PCNL1

PTMR2 PCSR2 PDUT2 PCNH2 PCNL2

0

1

2

3 PTMR3 PCSR3 PDUT3 PCNH3 PCNL3

PPG0

PPG1

PPG2

PPG3

Register number

IRQF PCNL: bit4

0

1

No interrupt request

Interrupt request

Write 0: Flag clear

OR

1

0

PPG1

interrupt

request

PPG2/3

interrupt

(#114/#115)

OR

PPG2

interrupt

request

PPG3

interrupt

request

PPG0

interrupt

request

IREN PCNL: bit5

0

1

Interrupt disabled

Interrupt enabled

PPG0/P17.0

PPG1/P17.1

PPG2/P17.2

PPG3/P17.3

0

1

From Port

Data register

Port read

Output level

(Latch)

PPG0

PPG1

PPG2

PPG3

PFR4: bit0

PFR4: bit1

PFR4: bit2

PFR4: bit3

0

1

General-purpose port

PPG output

PPG0/1

interrupt

(#112/#113)