772

Chapter 37 Output Compare

7.Q & A

7.11 How do I enable interrupts?

Enabling of interrupts is done with interrupt request permission bit (OCS01. ICE[1:0]), (OCS23. ICE[1:0]),

(OCS45. ICE[1:0]), (OCS67. ICE[1:0]).

Interrupt requests are cleared with interrupt request bits (OCS01. ICP[1:0]), (OCS23. ICP[1:0]), (OCS45.

ICP[1:0]), (OCS67. ICP[1:0]).

7.12 Compare value calculation procedure

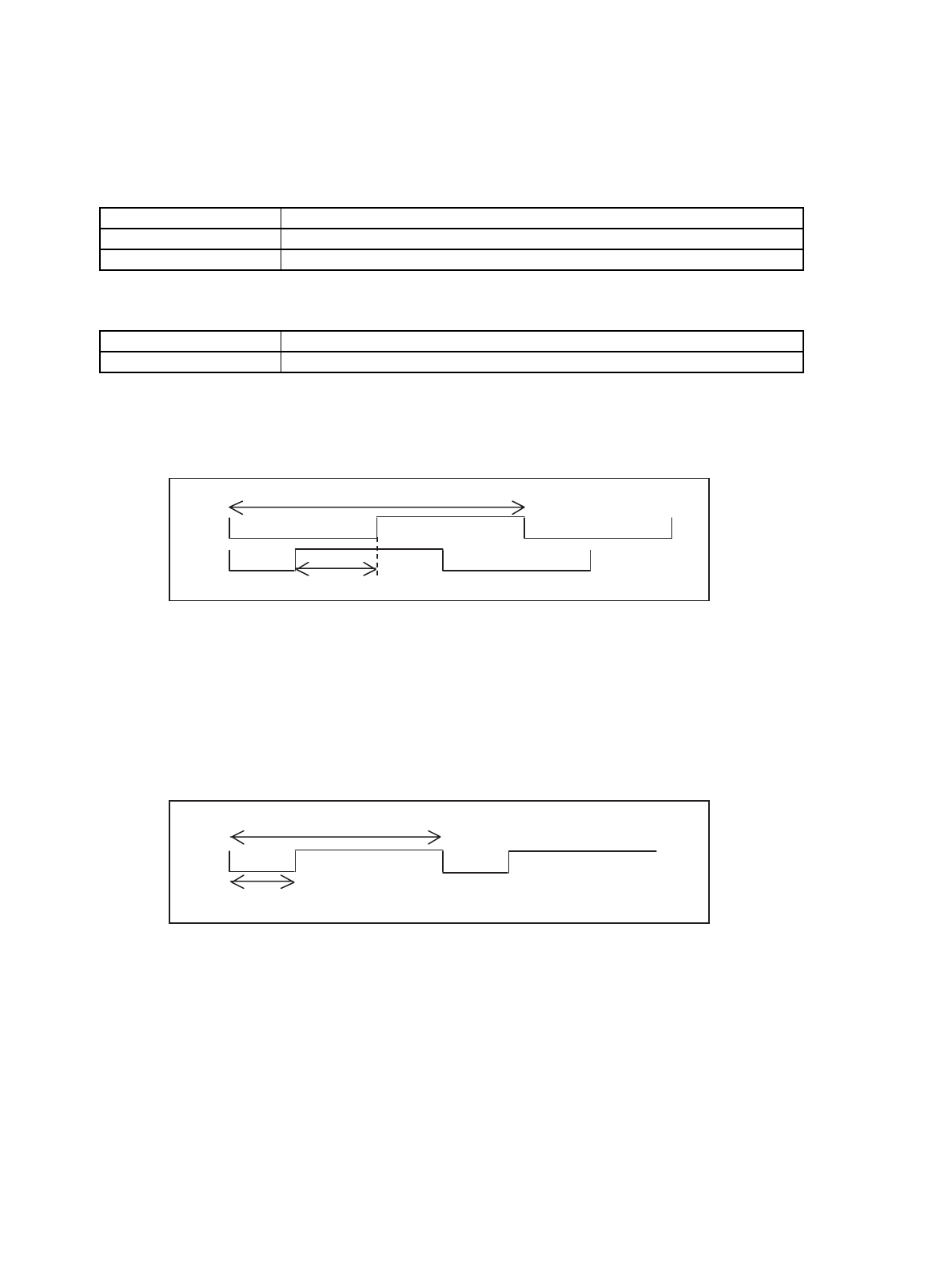

• Toggle output pulse

(Example) To output a period: A, phase difference 1/4 phase pulse

Formula:Compare 0 value = (A/2) / count clock

Compare 1 value = (A/4) / count clock

(Count clock: time set with free-run timer)

Note: To clear free-run timer 2 on compare 0 match setting (TCCS2.MODE=“1”) and CMOD=“0” setting are necessary.

Calculation example: A=1024us, count clock =125ns

Compare 0 value = (1024000 / 2) / 125 - 1 = 4095 = FFFh

Compare 1 value = (1024000 / 4) / 125 - 1 = 1023 = 7FFh

• PWM output

(Example) To output a period: A, duty 1/4 - 3/4 (“L”) PWM,

Formula: Compare 0 value = A / count clock

Compare 1 value = (A/4) / count clock (when duty 1/4)

(A x 3/4) / count clock (when duty 3/4)

(count clock: time set with free-run timer)

Note: To clear free-run timer 0 on compare 0 match setting (TCCS0.MODE=“1”) and CMOD=“1” setting are necessary.

Calculation example: A=1024us, count clock =125ns

Compare 0 value = 1024000 / 125 - 1 = 8191 = 1FFFh

Compare 1 value = (1024000 / 4) / 125 - 1 = 1023 = 7FFh (when duty 1/4)

(1024000 x 3 / 4) / 125 - 1 = 1023 = BFFh (when duty 3/4)

Interrupt request permission bit (ICE0, ICE1)

Interrupt disabled Set to “0”

Enable interrupts Set to “1”

Interrupt request bit (ICP0, ICP1)

Interrupt request clear Write “0”

OP0

OP1

1/4

A

OCU0

OCU1

Phase difference 1/4

A

OP1

1/4-3/4

A

OCU1

1/4-3/4

A