417

Chapter 29 MPU / EDSU

4.Registers

● EDSU Instruction Address Capture Register (BIAC)

This register captures the address of the instruction (IA), which has caused the protection violation or the operand/

data value break. This register could be read only.

● EDSU Operand Address Capture Register (BOAC)

This register captures the address of the operand access (OA), which has caused the protection violation or the

operand/data value break. This register could be read only.

● EDSU Break Detection Interrupt Request Register (BIRQ)

BIRQ collects all break detection bits of all channels, regardless of the type configuration of each channel. The ac-

tual implementation consists of 8 groups of channels, that are 32 single point channels totally.

Each group of channels consists of 4 channels and 4 bits for break detection in the BIRQ register. Each group has

two comparator pairs. Each pair consists of two point comparators which could build a range comparator by setting

the range enable bit. Such a range comparator pair is connected to the instruction address, operand address or the

data value information - selected by the comparator type configuration.

For detection of combined operand address and data value breaks two of such comparator pairs are combined to-

gether. Than the break detection (BD) bits are set only if both conditions are matching simultaneously.

BIT[31:0]: BD[31:0] - Break Detection register

BD[31:0] reflects the status of the break detection. It is set to ’1’ at match with BAD31...BAD0 accordingly (and if

the mask condition is satisfied, if enabled by EM1/0). For bit pairs [31:30], [29:28], ..., [1:0] range matches could

apply, if the range function using two points is enabled by ER1/0.

Break factors could be

• instruction address break,

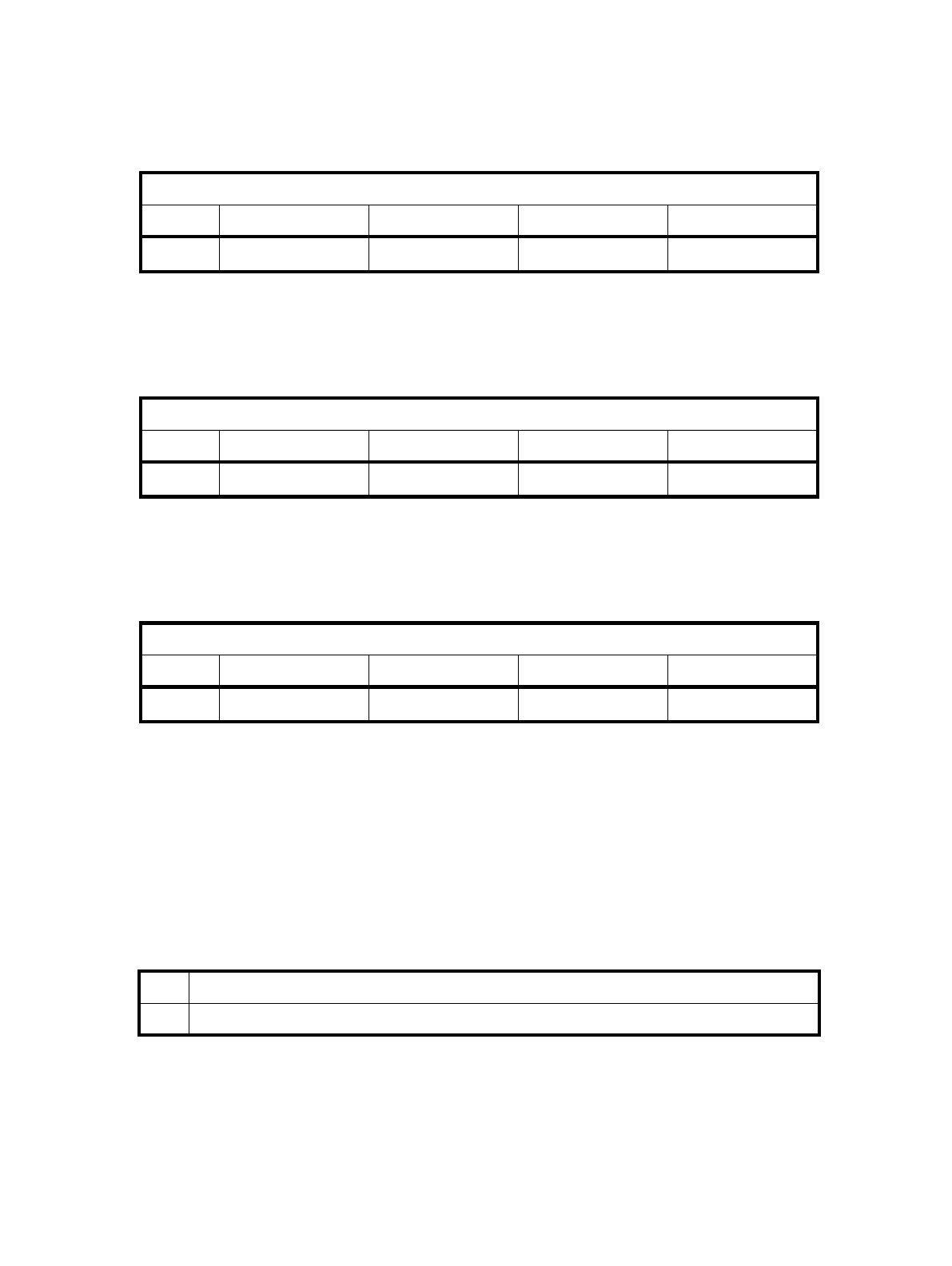

BIAC [R]

Address +0 +1 +2 +3

F008

H

00000000 00000000 00000000 00000000

BOAC [R]

Address +0 +1 +2 +3

F00C

H

00000000 00000000 00000000 00000000

BIRQ [R/W]

Address +0 +1 +2 +3

F010

H

00000000 00000000 00000000 00000000

0 Break factor not detected (default)

1 Break factor detected on channel according the bit position [31:0]