277

Chapter 20 Software Watchdog Timer

4.Register

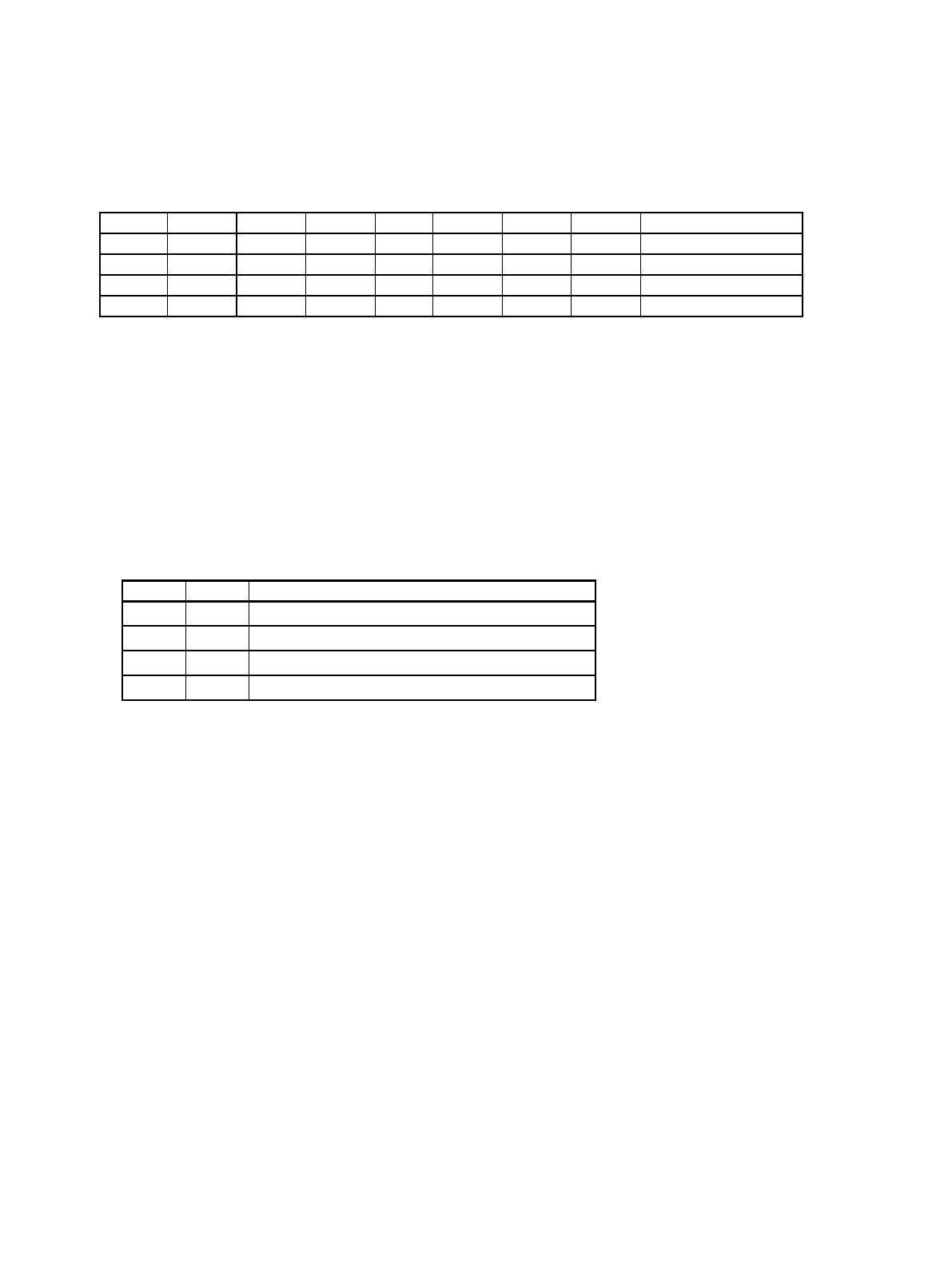

4.2 WPR: Watchdog Reset Generation Postponement Register

This register is used to postpone the generation of watchdog reset.

• WPR: Address 0485h (Access: Byte)

(Refer to “Meaning of Bit Attribute Symbols (Page No.10)” for the attributes.)

• If “A5

H

” and “5A

H

” are successively written in the watchdog reset generation postponement register and

immediately after writing “5A

H

” the 1-bit counter used to detect the watchdog is set to “0” to postpone the

generation of a watchdog reset.

Although there are no restrictions on the write timings for “A5

H

” and “5A

H

”, if “A5

H

” and a value other

than “5A

H

” are written, “A5

H

” must be written again. If not, writing “5A

H

” does not set the 1-bit counter to

“0”.

• The read value is indefinite.

• Both “A5

H

” and “5A

H

” must be written within the specified interval as shown below to prevent the

watchdog reset from being generated. The intervals are shown in the following table according to the

watchdog interval time selection bit (RSRR.WT[1:0]).

4.3 CTBR: Timebase Counter Clear Register

This register is used to initialize the timebase counter.

• CTBR: Address 0483h (Access: Byte)

For more information, refer to “Chapter 19 Timebase Timer (Page No.263)”.

76543210 bit

D7 D6 D5 D4 D3 D2 D1 D0

X X X X X X X X Initial value (INIT)

X X X X X X X X Initial value (RST)

RX,W RX,W RX,W RX,W RX,W RX,W RX,W RX,W Attribute

WT1 WT0 Minimum interval required for writing data in WPR

00

Within Φ × 2

20

(Initial value)

01

Within Φ × 2

22

10

Within Φ × 2

24

11

Within Φ × 2

26