419

Chapter 29 MPU / EDSU

4.Registers

● EDSU Channel Configuration Register (BCR0...BCR7)

For each group of four channels one channel configuration register (BCR0...BCR7) is implemented. It holds the con-

figuration set for the according group of channels. The following table shows the relationship, which channel con-

figuration, break point address/data registers and break detection bits belong together.

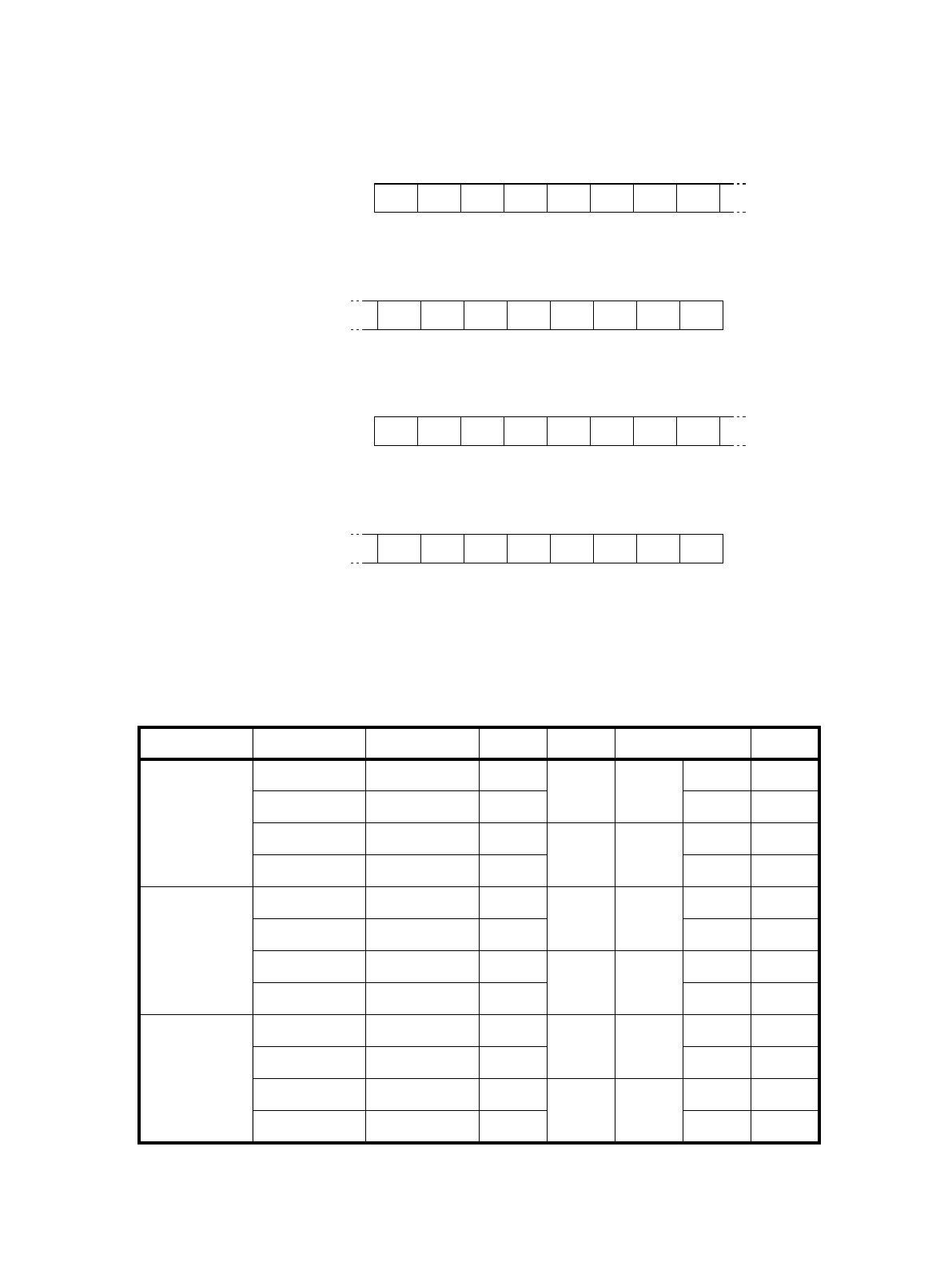

Table 4-3 Relationship of BCR, BAD and BIRQ registers

Group Config Address/Data BADx Usage Point Mask Combination BIRQ

BCR0 BAD0

Point0, Mask0 EP0 EM0 range 0

ER0

OA0

BD0

BAD1

Point1 EP1

OA1

BD1

BAD2

Point2, Mask1 EP2 EM1 range 1

ER1

DT0

BD2

BAD3

Point3 EP3

DT1

BD3

BCR1 BAD4

Point0, Mask0 EP0 EM0 range 0

ER0

OA0

BD4

BAD5

Point1 EP1

OA1

BD5

BAD6

Point2, Mask1 EP2 EM1 range 1

ER1

DT0

BD6

BAD7

Point3 EP3

DT1

BD7

BCR2 BAD8

Point0, Mask0 EP0 EM0 range 0

ER0

OA0

BD8

BAD9

Point1 EP1

OA1

BD9

BAD10

Point2, Mask1 EP2 EM1 range 1

ER1

DT0

BD10

BAD11

Point3 EP3

DT1

BD11

--------

⇐ Bit no.

Read/write ⇒

(-) (-) (-) (-) (-) (-) (-) (-)

Default value⇒

(X) (X) (X) (X) (X) (X) (X) (X)

EDSU Ch. Config Register 0, byte 0

Address : F020

H

31 30 29 28 27 26 25 24

SRX1 SW1 SRX0 SW0 URX1 UW1 URX0 UW0

⇐ Bit no.

Read/write ⇒

(R/W) (R/W) (R/W)

(R/W) (R/W) (R/W) (R/W) (R/W)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address :

F0

21H

23 22 21 20 19 18 17 16

EDSU Ch. Config Register 0, byte 1

MPE COMB CTC1 CTC0 OBS1 OBS0 OBT1 OBT0

⇐ Bit no.

Read/write ⇒

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

EDSU Ch. Config Register 0, byte 2

Address : F022

H

15 14 13 12 11 10 9 8

EP3 EP2 EP1 EP0 EM1 EM0 ER1 ER0

⇐ Bit no.

Read/write ⇒

(R/W) (R/W) (R/W)

(R/W) (R/W) (R/W) (R/W) (R/W)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address :

F0

23H

765432 10

EDSU Ch. Config Register 0, byte 3