404

Chapter 29 MPU / EDSU

3.Break Functions

On break both BD0 and BD2, respective BD1 and BD3 are set. They have to be reset by software in the operand

break exception routine.

3.5 Memory Protection

Due to the availability of address range comparators for the operand and instruction addresses the wish is obvios,

to use the same comparator hardware as a memory protection unit (MPU).

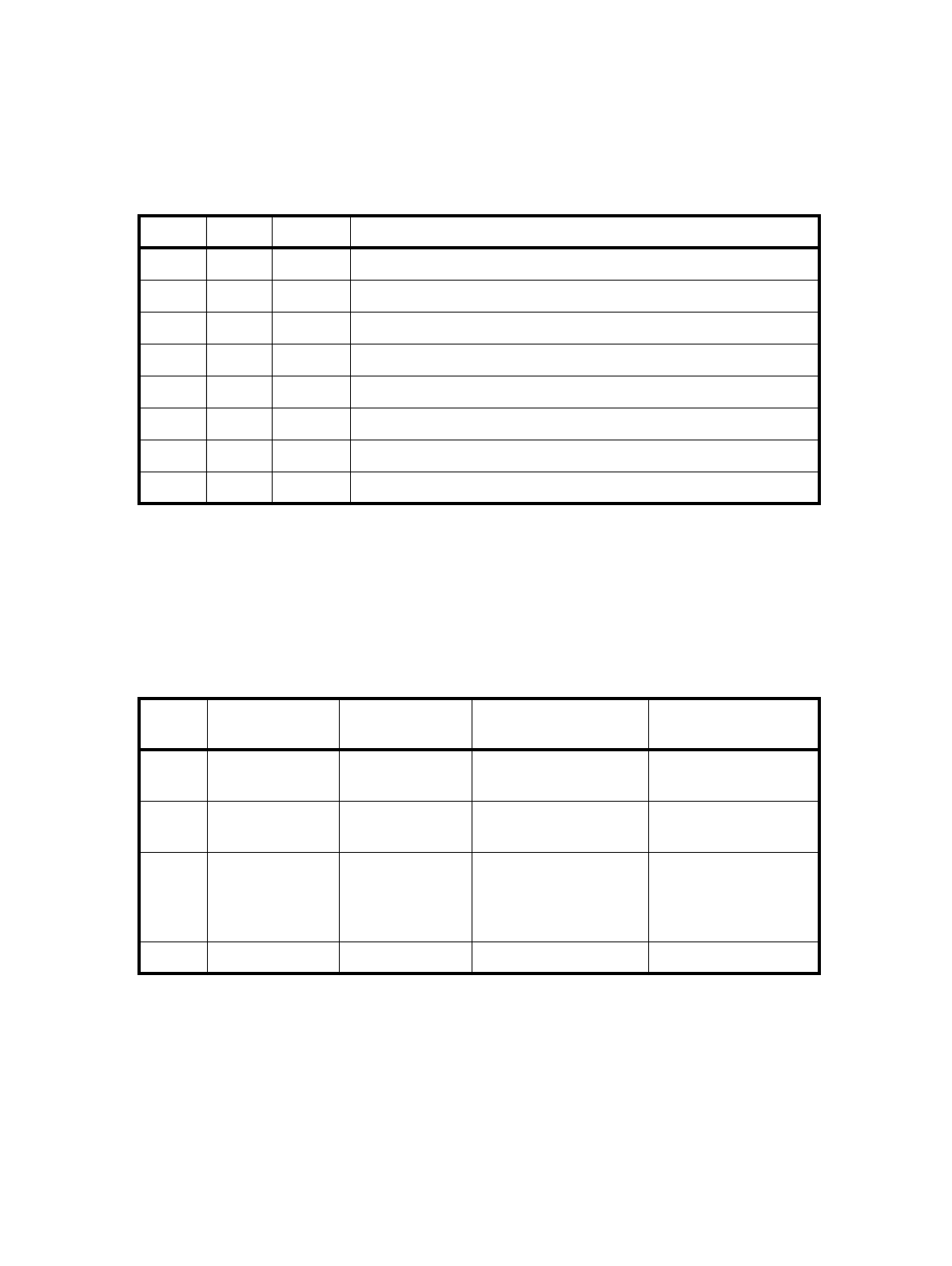

Following table list the possible type configurations and its feasibility to be used for memory protection. The number

of break points and MPU channels is valid for 8 comparator groups implemented.

Additional to the given hardware there were made some extensions to provide the user with a more likely configu-

ration of read, write and execute permissions instead of the more bus applicable definition of the operand break size

and type definitions OBS/OBT, including read-modify-write. With the introduction of the SuperVisor mode a defini-

tion of User and SuperVisor permissions is possible.

Table 3-5 Operand address and data value break combinations

EP3/2 EP1/0 COMB Function

0 0 0 No break detection

0 1 0 Independent data break (match value on any operand address)

1 0 0 Independent Operand break (match operand address)

1 1 0 Independent Data break and Operand break

0 0 1 No break detection

0 1 1 No break detection

1 0 1 No break detection

1 1 1 Data value break (match both operand address and value)

Table 3-6 Comparator Type Configuration

CTC CMP1 Input CMP0 Input Max. Break Points

(MPE=0)

Max. MPU Channels

(MPE=1)

00 IA IA 32 Instruction breaks 16 ranges with execute

permissions

01 OA OA 32 Operand breaks 16 ranges with read/

write permissions

10 OA IA 16 + 16 IA/OA breaks 8 ranges with read/

write and execute per-

missions or 8+8 inde-

pendent ranges

11 OA DT 16 data value breaks -