645

Chapter 32 USART (LIN / FIFO)

6.USART Baud Rates

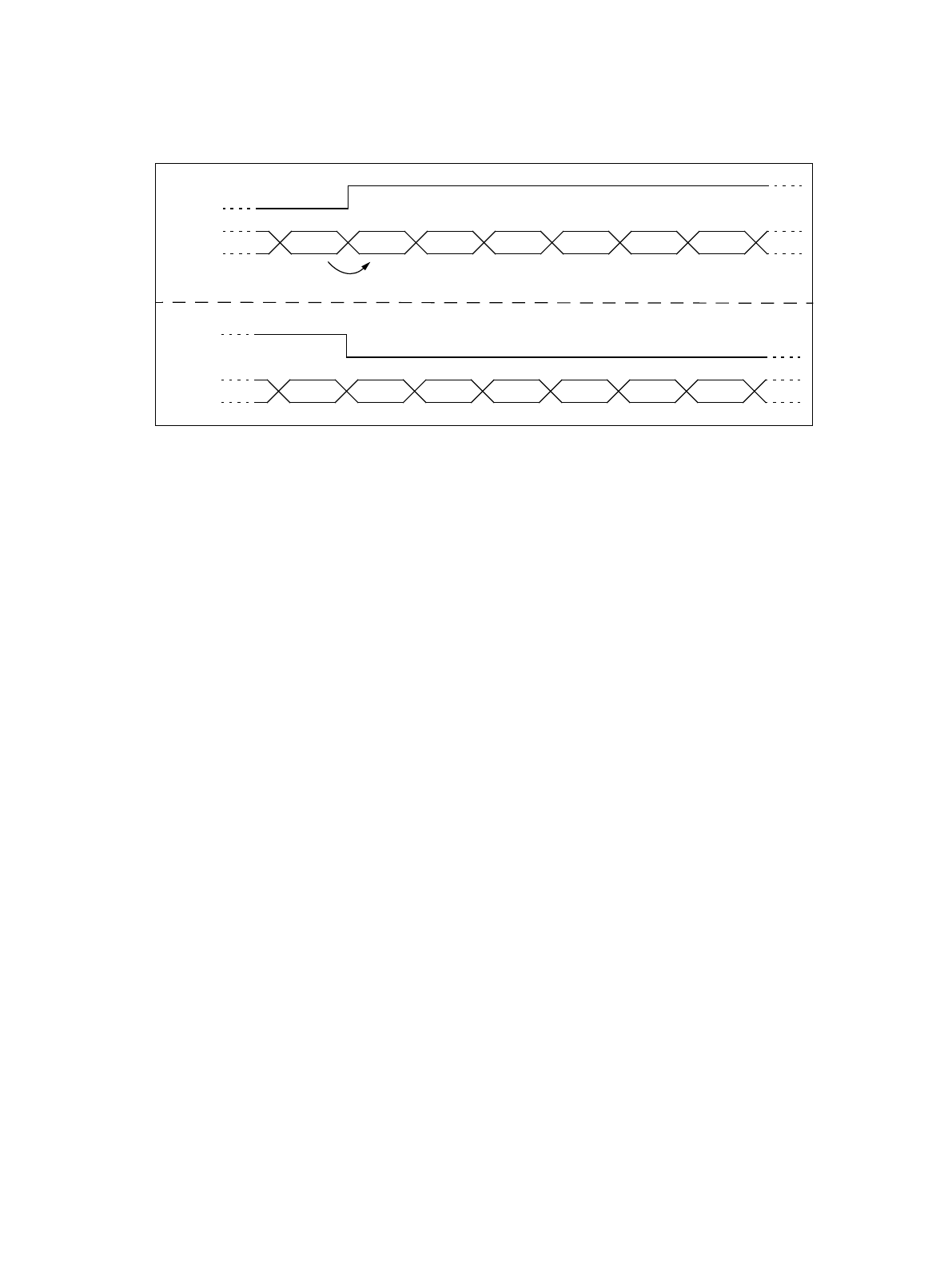

Figure 6-2 Counting example of the reload counters

(Note) The falling edge of the Serial Clock Signal always occurs after | (v + 1) / 2 |.

6.2 Restarting the Reload Counter

The Reload Counter can be restarted because of the following reasons:

Transmission and Reception Reload Counter:

• Global MCU Reset

• USART programmable clear (SMR04:UPCL bit)

• User programmable restart (SMR04: REST bit)

Reception Reload Counter:

• Start bit falling edge detection in asynchronous mode

■ Programmable Restart

If the REST bit of the Serial Mode Register (SMR04) is set by the user, both Reload Counters are restarted at

the next clock cycle. This feature is intended to use the Transmission Reload Counter as a small timer.

The following figure illustrates a possible usage of this feature (assume that the reload value is 100.)

001 000 832 831 830 829 828 827

Transmission/

Reload

Count

417 416 415 414 413 412 411 410

Transmission/

Reload

Count

reload count value

Reception Clock

Reception Clock