943

Chapter 48 Clock Monitor

4.Register

4. Register

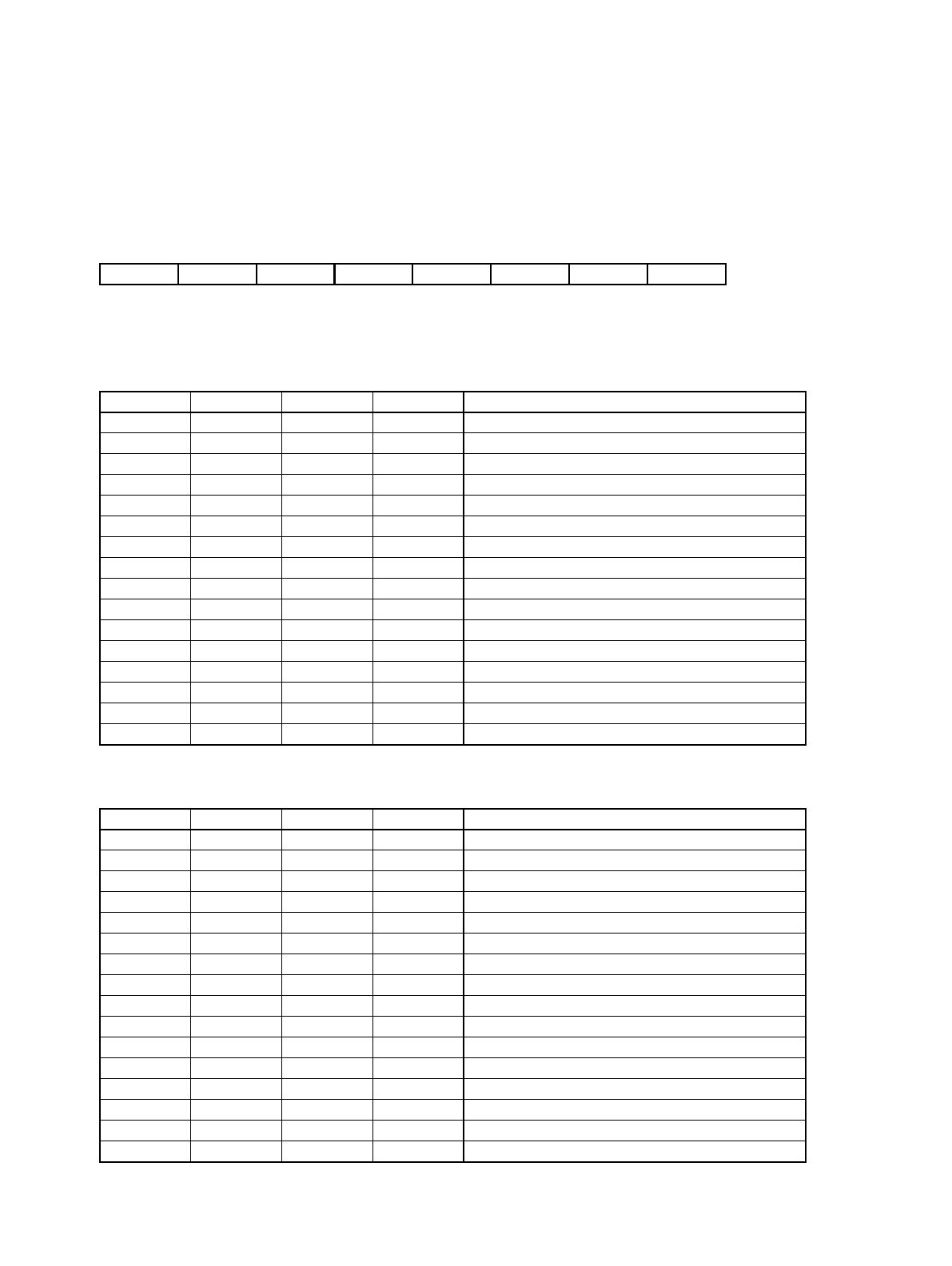

4.1 Clock Monitor Configuration Register

A register for output settings of an internal clock signal

• CMCFG: Address 04AF

H

(Access: Byte)

(For attributes, refer to “Meaning of Bit Attribute Symbols (Page No.10)”.)

• bit7-4: Select an output frequency prescaler

Specifies the frequency of a clock signal output to a clock monitor terminal.

• bit3-0: Select an output frequency prescaler

76543210bit

CMPRE3 CMPRE2 CMPRE1 CMPRE0 CMSEL3 CMSEL2 CMSEL1 CMSEL0

00000000Initial value

R/W R/W R/W R/W R/W R/W R/W R/W Attributes

CMPRE3 CMPRE2 CMPRE1 CMPRE0 Clock Frequency Output to the MONCLK pin

0000Source clock (selected by CMSEL) divided by 1 (Initial)

0001Source clock (selected by CMSEL) divided by 2

0010Source clock (selected by CMSEL) divided by 3

0011Source clock (selected by CMSEL) divided by 4

0100Source clock (selected by CMSEL) divided by 5

0101Source clock (selected by CMSEL) divided by 6

0110Source clock (selected by CMSEL) divided by 7

0111Source clock (selected by CMSEL) divided by 8

1000Source clock (selected by CMSEL) divided by 9

1001Source clock (selected by CMSEL) divided by 10

1010Source clock (selected by CMSEL) divided by 11

1011Source clock (selected by CMSEL) divided by 12

1100Source clock (selected by CMSEL) divided by 13

1101Source clock (selected by CMSEL) divided by 14

1110Source clock (selected by CMSEL) divided by 15

1111Source clock (selected by CMSEL) divided by 16

CMSEL CMSEL2 CMSEL1 CMSEL0 Clock Source Output to the MONCLK pin

0000MONCLK output disabled (high impedance) (Initial)

0001Main oscillation before clock supervisor

0010Sub oscillation before clock supervisor

0011RC oscillation

0100Sub clock (after sub clock selector SCKS)

0101Main oscillation after clock supervisor (MCLK_OUT)

0110Sub oscillation after clock supervisor (SCLK_OUT)

0111Clock modulator output to Clock Control

1000Clock modulator observer output

1001PLL output after 1/g divider (Auto Gear)

1010PLL output after 1/m divider (PLL output)

1011PLL output after 1/c divider (CAN clock)

1100PLL input after 1/n divider (PLL feedback)

1101CLKB

1110CLKP

1111CLKT