673

Chapter 33 I2C Controller

2.I2C Interface Registers

2.2 Bus Status Register (IBSR0)

The bus status register (IBSR0) has the following functions:

• Bus busy detection

• Repeated start condition detection

• Arbitration loss detection

• Acknowledge detection

• Data transfer direction indication

• Addressing as slave detection

• General call address detection

• Address data transfer detection

This register is read-only, all bits are controlled by the hardware. All bits are cleared if the interface is not

enabled (EN=‘0’ in ICCR0).

[bit 7] BB (Bus Busy)

This bit indicates the status of the I

2

C bus.

This bit is set to ‘1’ if a start condition is detected. It is reset upon a stop condition.

[bit 6] RSC (Repeated Start Condition)

This bit indicates detection of a repeated start condition.

This bit is cleared at the end of an address data transfer (ADT=‘0’) or detection of a stop condition.

[bit 5] AL (Arbitration Loss)

This bit indicates an arbitration loss.

This bit is cleared by writing ‘0’ to the INT bit or by writing ‘1’ to the MSS bit in the IBCR0 register.

An arbitration loss occurs if:

• the data sent does not match the data read on the SDA line at the rising SCL edge

0 Stop condition detected (bus idle).

1 Start condition detected (bus in use).

0 Repeated start condition not detected.

1 Bus in use, repeated start condition detected.

0 No arbitration loss detected.

1 Arbitration loss occurred during master sending.

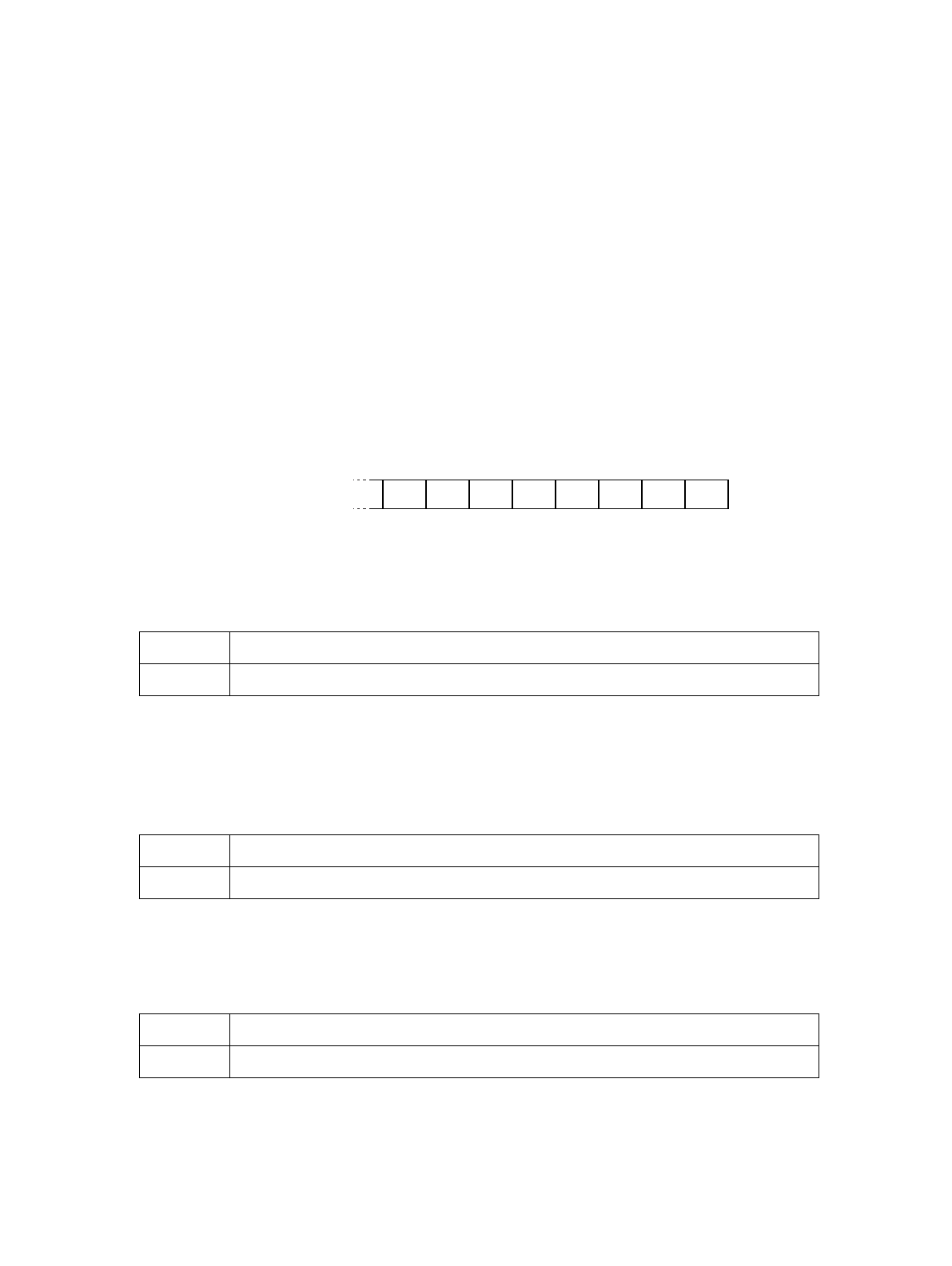

BB RSC AL LRB TRX AAS GCA ADT

⇐ Bit no.

Read/write ⇒

(R) (R) (R) (R) (R) (R) (R) (R)

Default value⇒

(0) (0) (0) (0) (0) (0) (0) (0)

Address : 0000D1

H

765432 10

IBSR0

Bus status register