295

Chapter 22 Main Oscillation Stabilisation Timer

7.Q & A

7. Q & A

7.1 What are the types of interval time (wait time) and how are they selected?

There are 3 types of interval time, and they are set with the interval selection bit (OSCRH.WS[0:1]).

Note: Setting (WS[1:0]=“00”) is prohibited.

7.2 How do I select the count clock?

The count clock is the main clock (source oscillation). (Cannot be selected.)

7.3 How is the main clock oscillation stability wait timer count operation enabled/

disabled?

Sets with the timer operation enable bit (OSCRH.WEN).

7.4 How is the main clock oscillation stability wait timer cleared?

The following methods are used to clear the main clock oscillation stability wait timer.

• Sets with the clear bit (OSCRH.WCL).

• Performs a reset.

Clears the free run timer with the operation initialization reset (INIT terminal input, watchdog reset).

(Value is held without being cleared even if a software reset is performed.)

• The overflow (Next of “FFFFFFh”) of the main clock oscillation stability wait timer causes the count value to

be reset to “000000

H

”.

7.5 What happens with the interrupt-associated registers?

Setting the interrupt vector and interrupt level of the main clock oscillation stability wait timer

The relationship between the interrupt level and the interrupt vector is shown in the following table.

Refer to “Chapter 24 Interrupt Control (Page No.311)” for the interrupt level and interrupt vector.

As the interrupt request flag (OSCRH.WIF) is not automatically cleared, clear it before returning to interrupt

processing by the software. (Writes “0” in the WIF bit.)

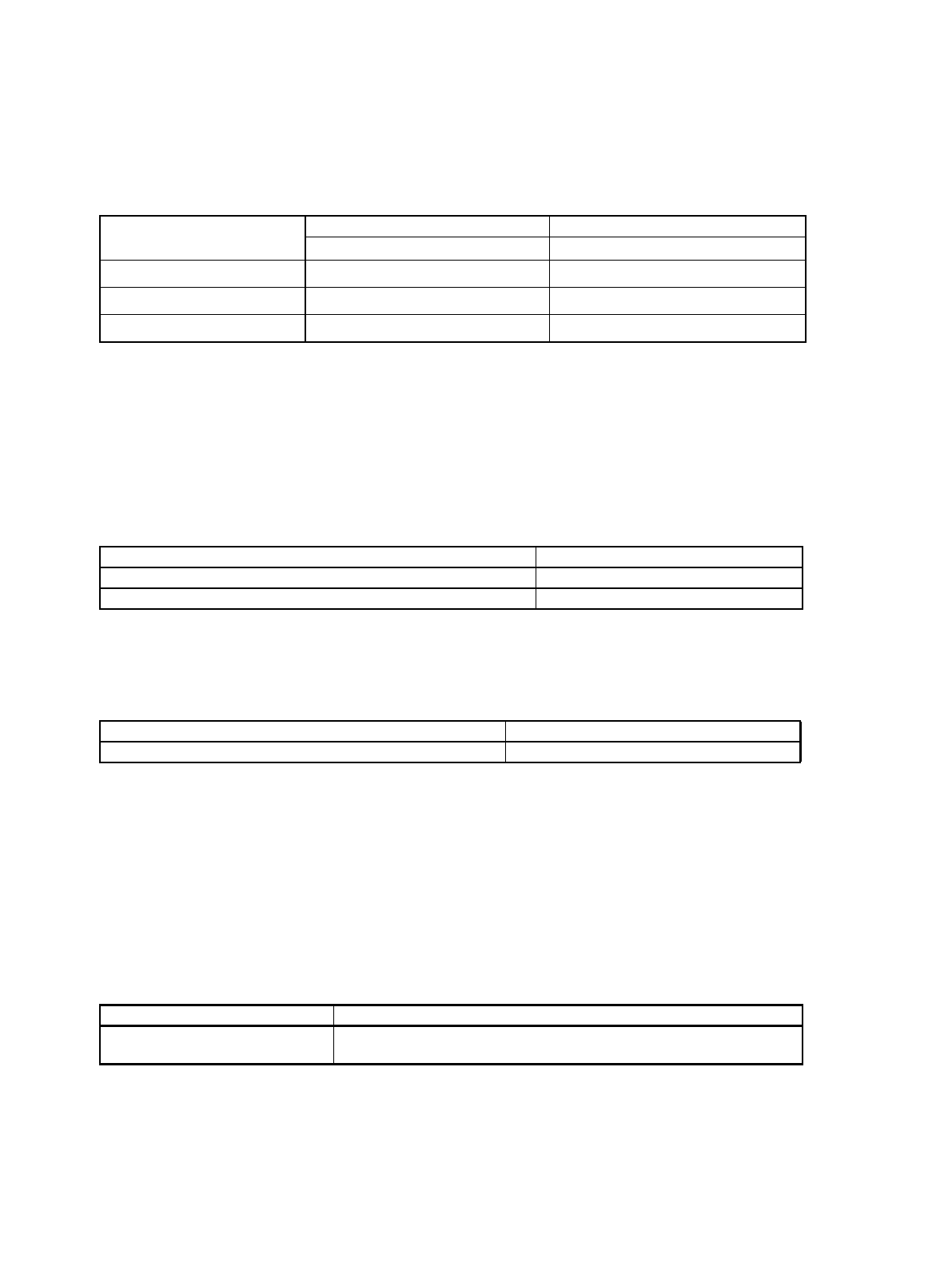

Interval time

Count period Interval (Wait time) Example

Interval selection bit (WS[1:0])

At F

CLKP

= 4.00MHz

To set the value to 2

12

/F

CL-MAIN

Set the value to “01” 1.00ms

To set the value to 2

17

/F

CL-MAIN

Set the value to “10” 32.7ms

To set the value to2

23

/F

CL-MAIN

Set the value to “11” 2.00 s

Operation Timer operation enable bit (WEN)

To stop the main clock oscillation stability wait timer Set the value to “0”

To start the main clock oscillation stability wait timer Set the value to “1”

Operation Clear bit (WCL)

To clear the main clock oscillation stability wait timer Writes “1”

Interrupt vector (Default) Interrupt level setting bit (ICR4-ICR0)

#143

Address: 0FFDC0h

Interrupt level register (ICR63)

Address: 047Fh