109

Chapter 4 CPU Architecture

7.Data Structure

7. Data Structure

FR60 has two data allocations as follows.

■ Bit Ordering

FR60 uses little endian as bit ordering.

Figure 7-1 Bit Structure of Bit Ordering

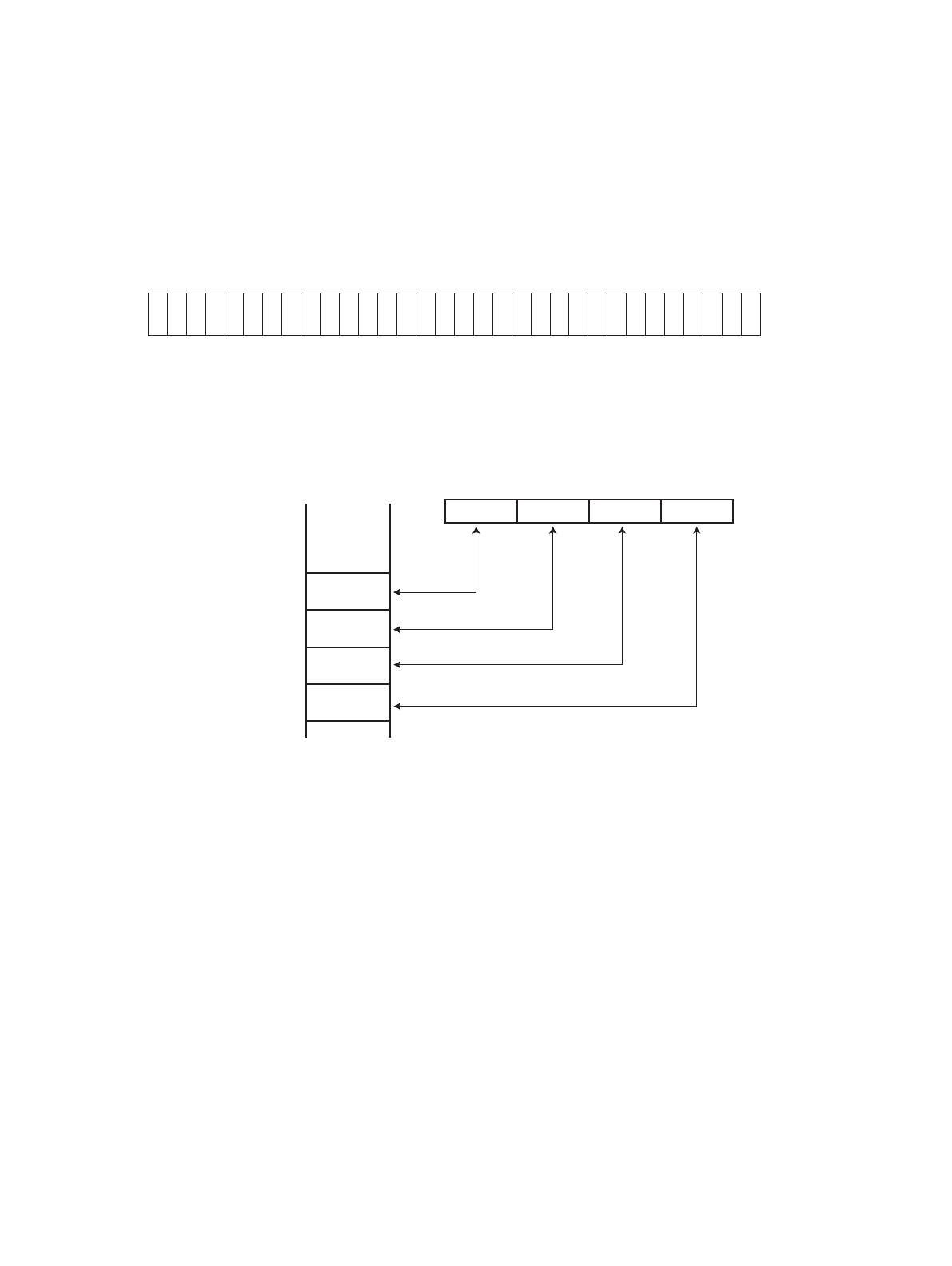

■ Byte Ordering

FR60 uses big endian as byte ordering.

Figure 7-2 Bit Structure of Byte Ordering

bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 1514 13 12 11 10 9 8 7 6 5 4 3

2

10

LSB

MSB

Memory

MSB

bit31 23 15 7

LSB

0

10101010

11001100

11001100

11111111

11111111

00010001

00010001

bit

7

0

10101010

n address

(n+1) address

(n+2) address

(n+3) address