352

Chapter 26 DMA Controller

2.DMA Controller (DMAC) Registers

DMA operation can be forced to stop by writing 0 to this bit. However, be sure to force stopping (0 write) only

after temporarily stopping DMA using the DMAH[3:0] bits [Bit27 to 24 of DMACR]. If forced stopping is carried

out without first temporarily stopping DMA, DMA stops, but the transfer data cannot be guaranteed. Check

whether DMA is stopped using the DSS[2:0] bits [Bit18 to 16 of DMACB].

• When reset: Initialized to 0.

• This bit is readable and writable.

[Bit 28] PM01 (Priority mode ch0,1 robine): Channel priority rotation

This bit is set to alternate priority for each transfer between Channel0 and Channel1.

• When reset: Initialized to 0.

• This bit is readable and writable.

[Bits 27 to 24] DMAH (DMA Halt): DMA temporary stop

These bits control temporary stopping of all DMA channels. If these bits are set, DMA transfer is not performed

on any channel before these bits are cleared.

When DMA transfer is activated after these bits are set, all channels remain temporarily stopped.

Transfer requests that occur on channels for which DMA transfer is enabled (DENB=1) while these bits are set

are all enabled. The transfer can be started by clearing all these bits.

• When reset: Initialized to 0.

• These bits are readable and writable.

[Bits 30, 29, and 23 to 0] (Reserved): Unused bits

These bits are unused.

• A read value is undefined.

2.5 Other Functions

The MB91460 series has the DACK, DEOP, and DREQ pins, which can be used for external

transfer. These pins can also be used as general-purpose ports.

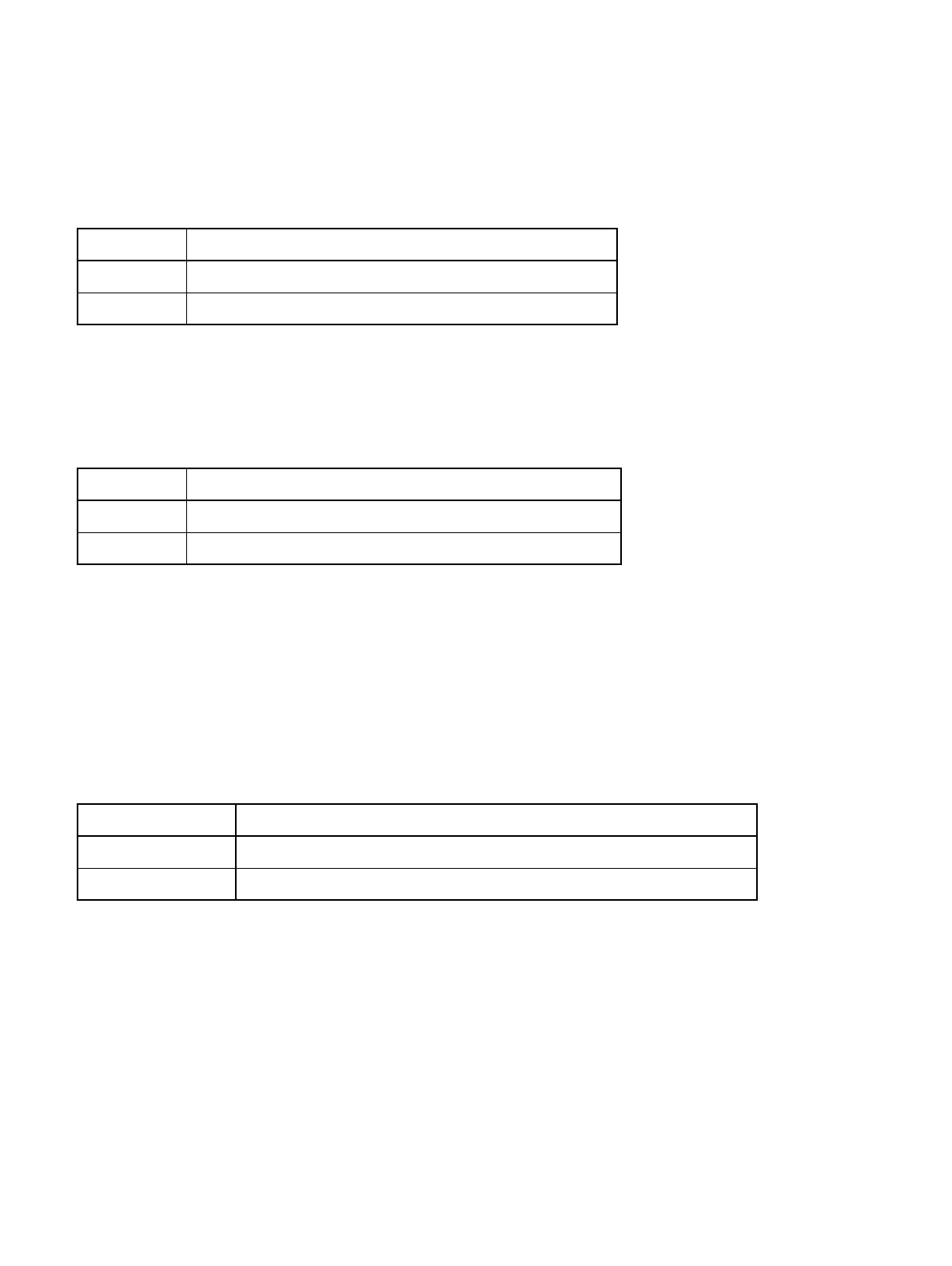

DMAE Function

0 Disables DMA transfer on all channels. (initial value)

1 Enables DMA transfer on all channels.

PM01 Function

0 Fixes the priority. (ch0 > ch1)(initial value)

1 Alternates priority. (ch1 > ch0)

DMAH Function

0000

B

Enables the DMA operation on all channels. (initial value)

Other than 0000

B

Temporarily stops DMA operation on all channels.