638

Chapter 32 USART (LIN / FIFO)

5.USART Interrupts

5. USART Interrupts

The USART uses both reception and transmission interrupts. An interrupt request can be generated for either

of the following causes:

• Receive data is set in the Reception Data Register (RDR04), or a reception error occurs.

• Transmission data is transferred from the Transmission Data Register (TDR04) to the transmission shift

register.

• A LIN break is detected

• No bus activity (neither reception nor transmission)

■ USART Interrupts

x : Used

* : Only available if ECCR04/SSM = 1

■ Reception Interrupt

If one of the following events occur in reception mode, the corresponding flag bit of the Serial Status Register

(SSR04) is set to "1":

• - Data reception is complete, i. e. the received data was transferred from the serial input shift register to the

Reception Data Register (RDR04) and data can be read: RDRF (if FIFO is enabled, trigger level is reached)

• - Overrun error, i. e. RDRF = 1 and RDR04 was not read by the CPU: ORE

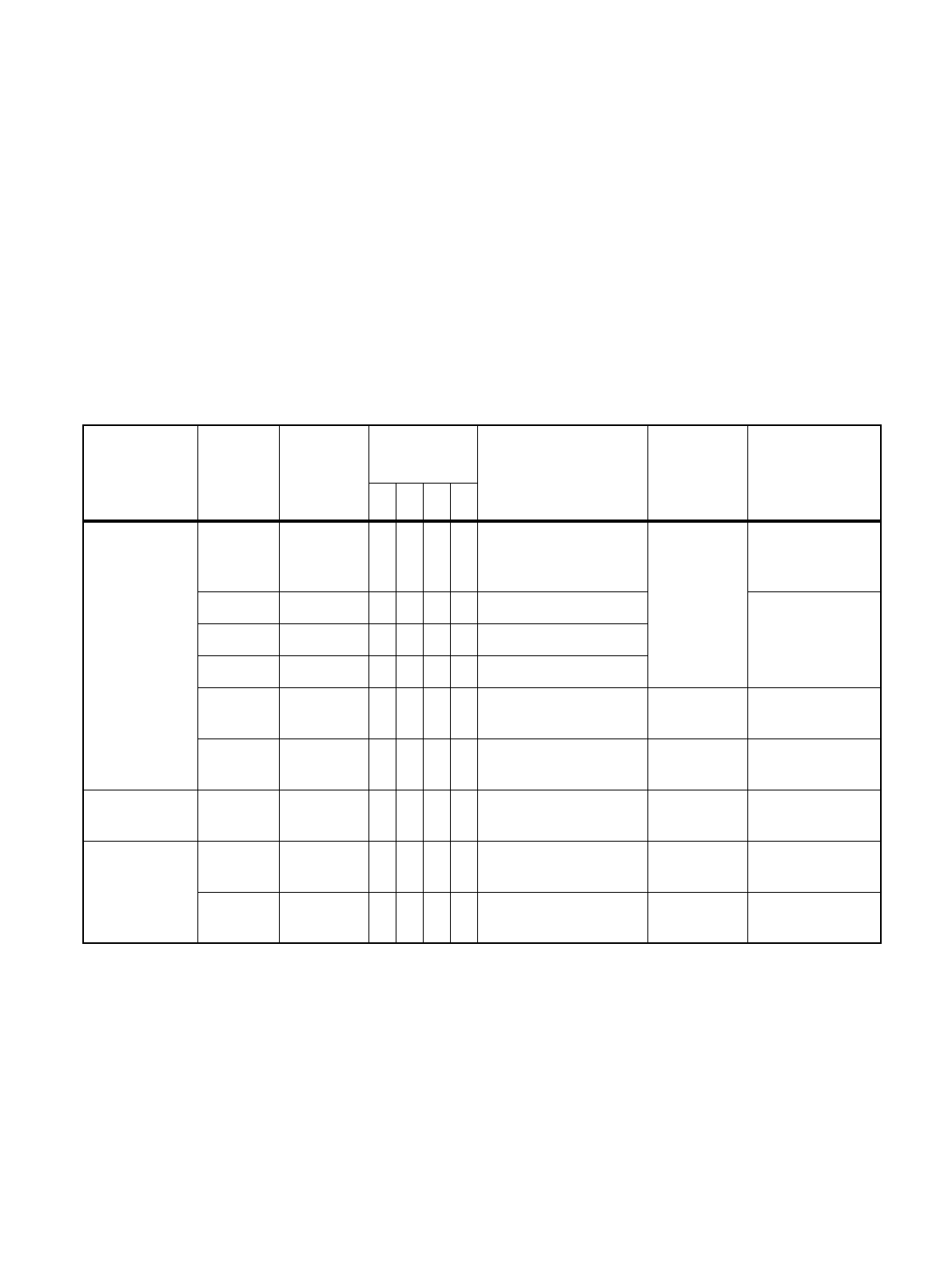

Table 5-1 Interrupt control bits and interrupt causes of USART

Reception/

transmission/

ICU

Interrupt

request

flag bit

Flag

Register

Operation

mode Interrupt

cause

Interrupt

cause

enable bit

How to clear

the Interrupt

Request

0123

Reception RDRF SSR04 xxxxreceive data is

written to RDR

(FIFO level reached)

SSR04 :

RIE

Receive data

is read

ORE SSR04 xxxxOverrun error "1" is written to

clear rec. error

bit (SCR04:

CRE)

FRE SSR04 x x * x Framing error

PE SSR04 x * Parity error

LBD ESCR04 x x LIN synch break

detected

ESCR04 :

LBIE

"0" is written to

ESCR04 : LBD

TBI &

RBI

ESCR04 x x x no bus activity ECCR04 :

BIE

Receive data /

Send data

Transmission TDRE SSR04 xxxxEmpty transmission

register

SSR04 :

TIE

Transfer data is

written

Input

Capture Unit

ICP4 IPCP4 x x 1st falling edge of

LIN synch field

IPCP4 :

ICE4

disable ICE4

temporary

ICP4 IPCP4 x x 5th falling edge of

LIN synch field

IPCP4 :

ICE4

disable ICE4