415

Chapter 29 MPU / EDSU

4.Registers

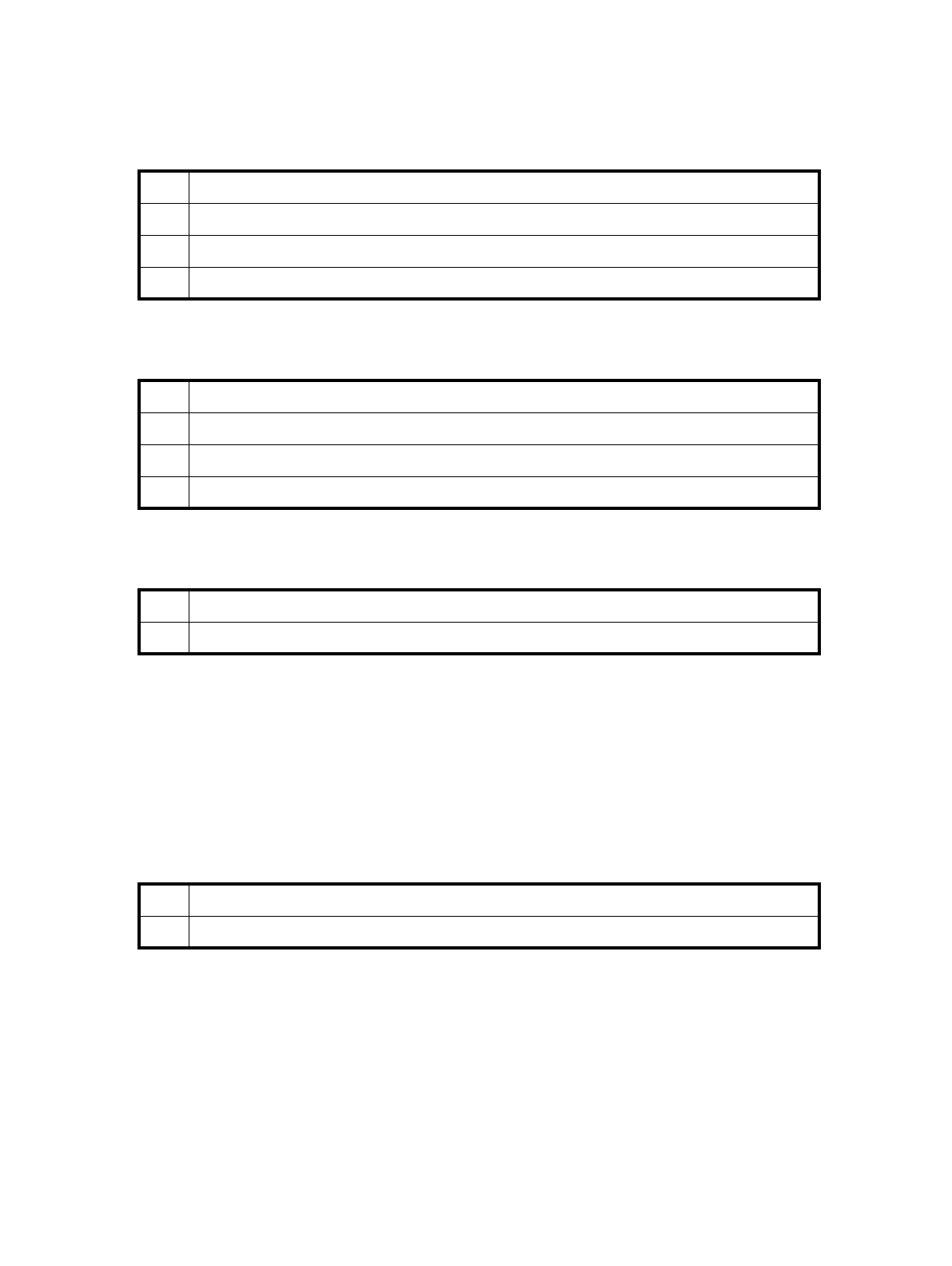

BIT[9:8]: CSZ[1:0] - Capture Operand Size

BIT[7:6]: CRW[1:0] - Capture Operand Access Type

BIT[5]: PV - Protection Violation Detection

If this bit is set after a protection violation, a MPUPV trap is indicated to the CPU. The occurance of a protection

violation means, that there was a read or write access to a defined address region, which was not permitted or code

was executed without execute permissions for this address region. As consequence the CPU switches to super vi-

sor mode (SV=1) and calls the handler routine for interrupt number #6 (see table 3-8).

This bit should be cleared by writing ’0’ in the MPUPV trap handler routine.

BIT[4]: RST - Operation Initialization Reset (RST) Detection

The reset operation of FRex family is divided into two levels, setting initialization reset (INIT) and operation initiali-

zation reset (RST). When INIT occurs, RST occures at the same time implicitely.

The RST bit is read only, any write access to this bit will be ignored. RST is cleared after BSTAT is read (read from

any byte address within the 32 bit word). RST has same behaviour for read and read-modify-write access.

The RST bit can be used for reset detection. It is set in any case of operation initialization reset is triggered. Debug

monitor software can use this to detect if the communication device to the debugger front end needs to be re-con-

figured after an operation reset. This is important for debugging of boot procedures and soft reset handling. After

reading the EDSU status word the RST bit is cleared automatically.

Break Interrupt Register

00 The operand has a bit size of 8

01 The operand has a bit size of 16

10 The operand has a bit size of 32

11 reserved

00 The operand has been read

01 The operand has been read by read-modify-write indicated

10 The operand has been written

11 no operand access

0 There was no protection violation on read, write and execute permissions

1 A protection violation (MPUPV) has been occured

0 Operation Reset was not triggered since last BSTAT read or clear

1 Operation Reset was triggered since last BSTAT read or clear